Sw3.6-l10-1.2-Slajd8

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

Sterownik TAP Laboratorium Wprowadzenie

Organizacja sterownika TAP

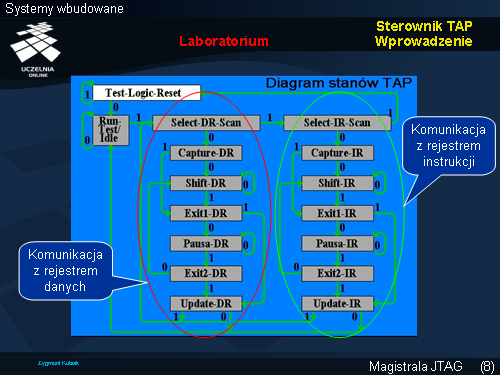

Cały proces szeregowego przesyłania informacji jest sterowany sygnałem TMS interpretowanym w sterowniku TAP (ang. Test Access Port controller ). Jest on jednowejściowym układem synchronicznymi o 16 stanach, w którym każda zmiana stanu następuje na narastającym zboczu TCK .

Sterownik TAP można wprowadzić w następujące stany:

- Test-Logic-Reset , w którym testowanie jest wyłączone, a układ pierwotny spełnia swoje normalne funkcje użytkowe;

- Run-Test/Idle , w którym następuje wykonanie autotestowania (Run-Test ) albo jest stanem spoczynkowym (Idle );

- komunikacji z rejestrem danych

- zapamiętanie odpowiedzi na test (Capture-DR ),

- szeregowe przesłanie odpowiedzi do testera (stany Shift-DR ) a jednocześnie wpisanie nowych pobudzeń,

- uaktualnienie kopii rejestru – podanie nowych pobudzeń (Update-DR );

- komunikacji z rejestrem instrukcji

- zapamiętanie statusu (Capture-IR ),

- szeregowe wysłanie statusu do testera (stany Shift-IR ) a jednocześnie wpisanie nowej instrukcji,

- uaktualnienie rejestru kopii – zmiana instrukcji (Update-IR );

- pomocnicze Exit ,

- Pause umożliwiające czasowe wstrzymanie komunikacji szeregowej, np. w celu pobrania/wpisu danych z/do zewnętrznej pamięci masowej.