TC Moduł 12

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

|

Projektowanie układów cyfrowych cz. 1 |

|

Sposób specyfikacji układów cyfrowych w języku opisu sprzętu przyjęło się klasyfikować jako tzw. style projektowania. Wyróżnia się styl behawioralny, strukturalny oraz przepływ danych. |

|

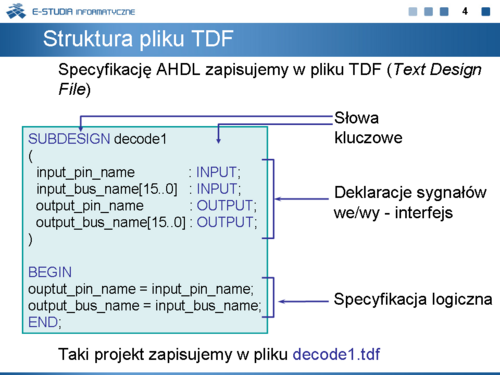

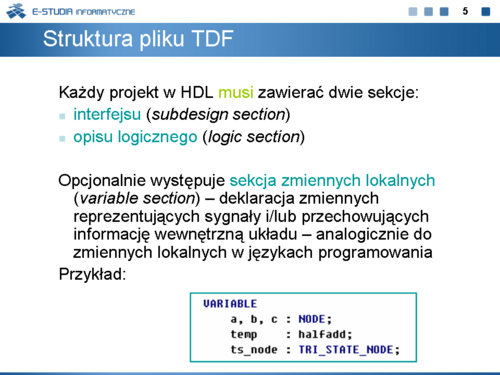

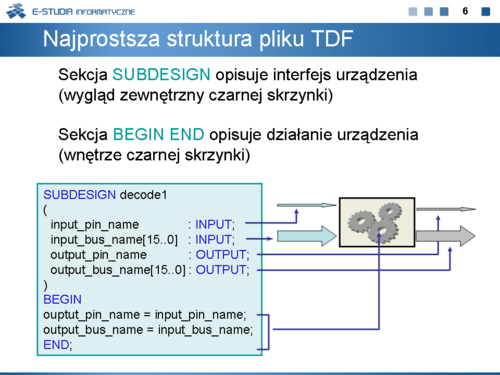

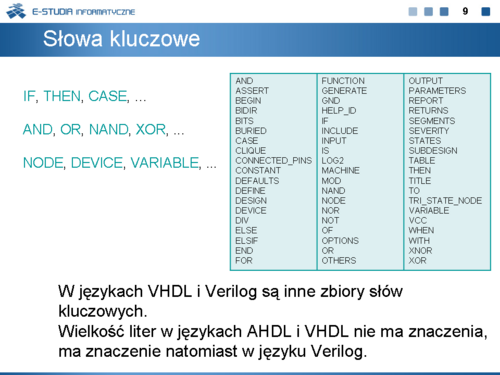

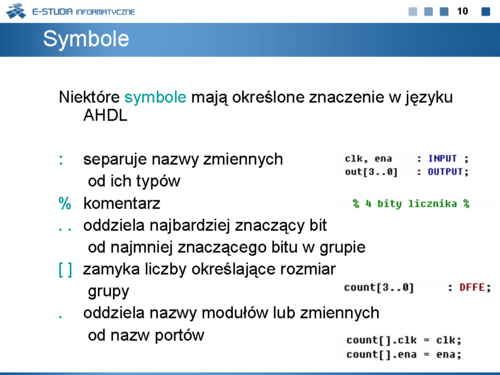

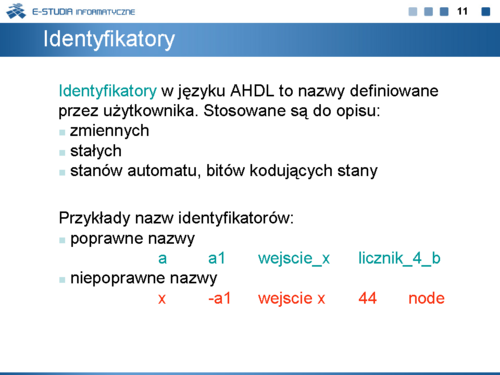

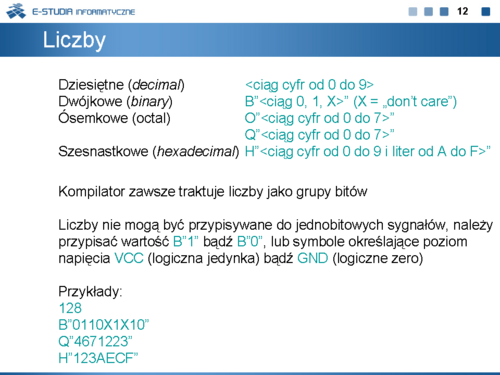

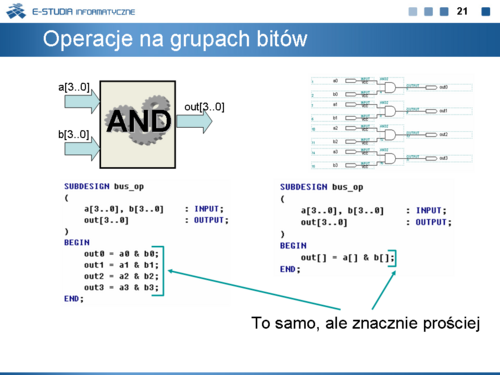

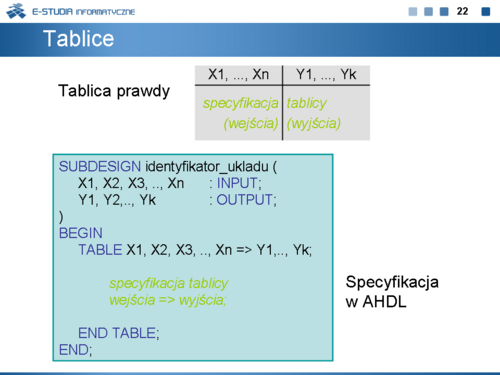

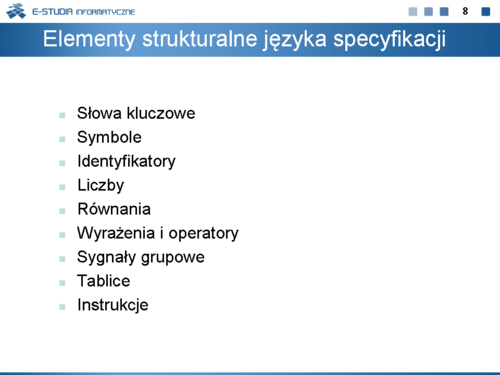

Elementami strukturalnymi języków HDL stosowanymi w opisie układów cyfrowych są przede wszystkim słowa kluczowe, równania, tablice, instrukcje itp. |

|

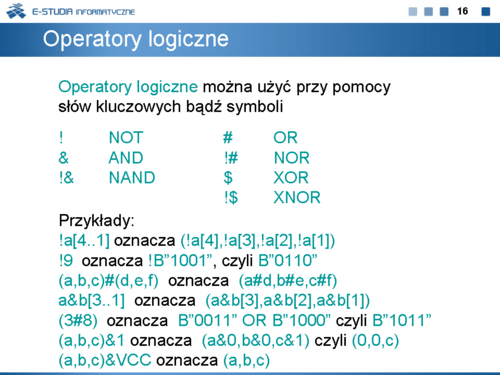

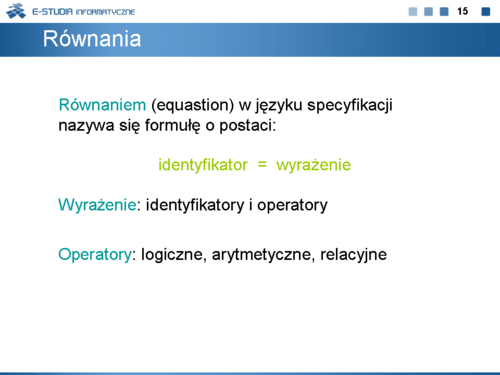

Podstawową konstrukcją do specyfikacji układów cyfrowych w języku AHDL są równania boolowskie. W równaniu występuje identyfikator, symbol przypisania oraz wyrażenie boolowskie.

|

|

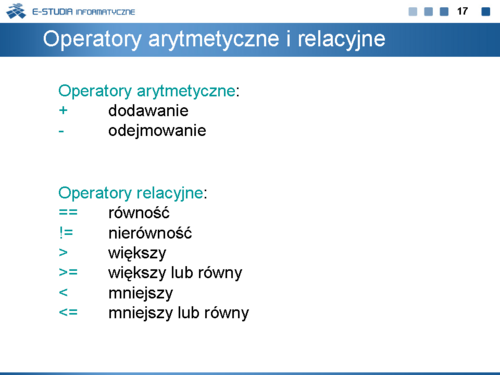

Do opisu działania typowych układów cyfrowych często stosowane są operatory arytmetyczne i relacyjne. |

|

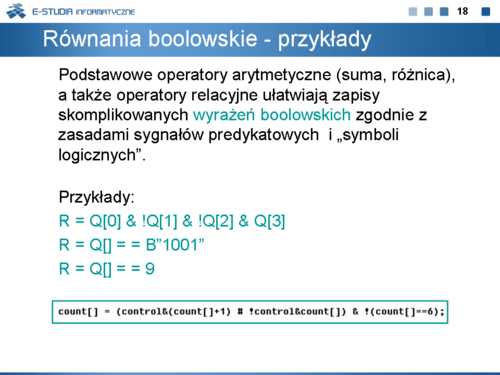

Podstawowe operatory arytmetyczne (suma, różnica), a także operatory relacyjne ułatwiają zapisy skomplikowanych wyrażeń boolowskich zgodnie z zasadami sygnałów predykatowych i „symboli logicznych”. |

|

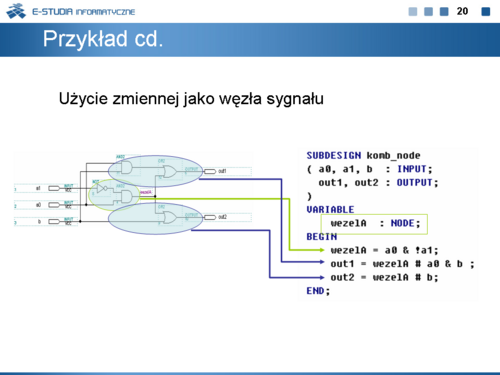

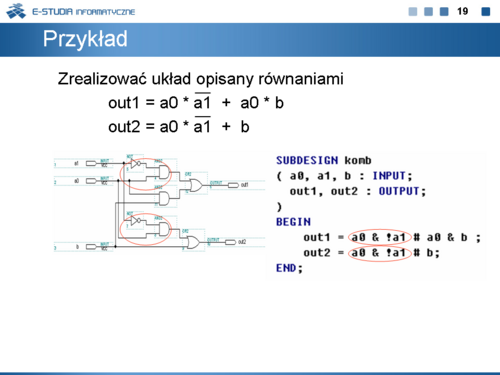

Typowe zastosowanie równań to specyfikacje układów logicznych zbudowanych z bramek. Rysunek na planszy przedstawia prosty układ kombinacyjny. Układ ten zapisany jest w języku AHDL w projekcie komb. |

|

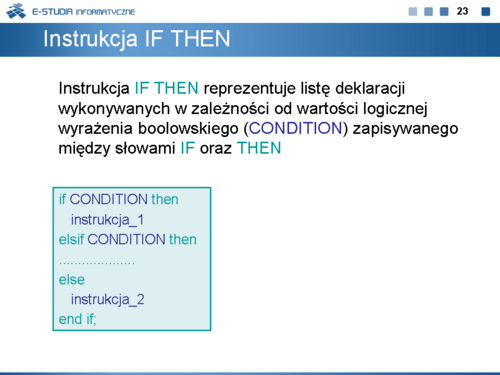

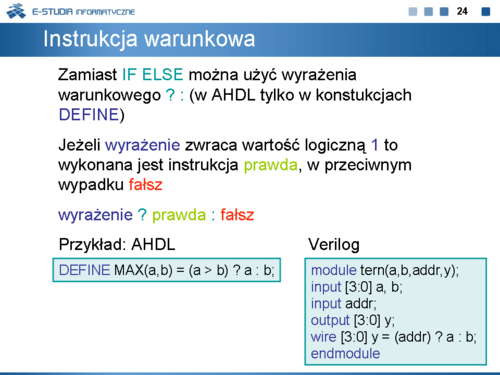

Analogiczną rolę jak instrukcja IF THEN spełnia wyrażenie warunkowe. |

|

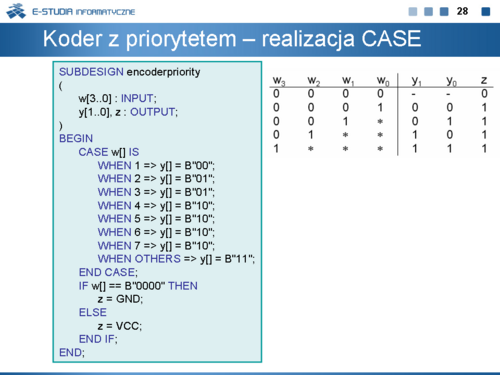

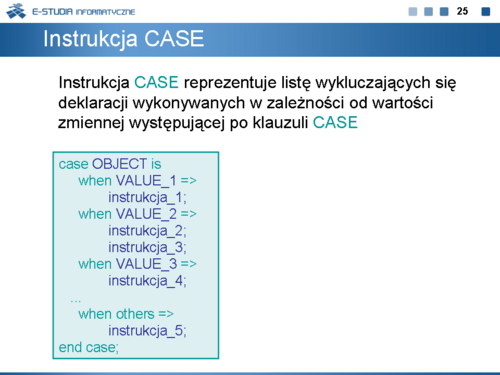

Instrukcja CASE reprezentuje listę wykluczających się deklaracji wykonywanych w zależności od wartości zmiennej występującej po klauzuli CASE. |

|

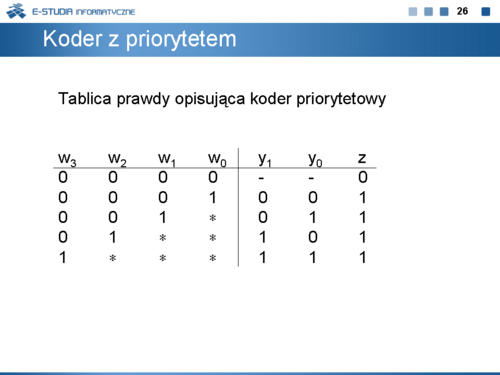

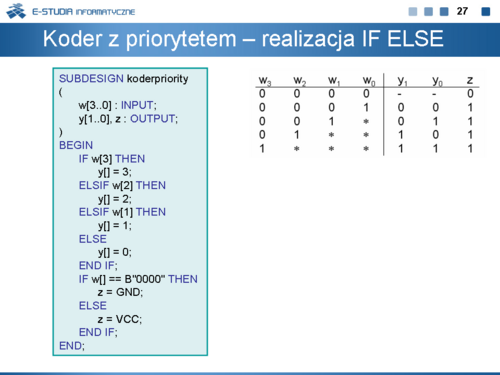

Doskonałym przykładem ilustrującym specyfikacje układów kombinacyjnych z zastosowaniem instrukcji IF THEN oraz CASE jest koder priorytetowy opisany tablicą prawdy podaną na planszy. |

|

Specyfikacja kodera instrukcją IF THEN jest wygodna o tyle, że wykorzystuje ona naturalne własności kodera, a mianowicie priorytet sygnału , następnie nad pozostałymi. |

|

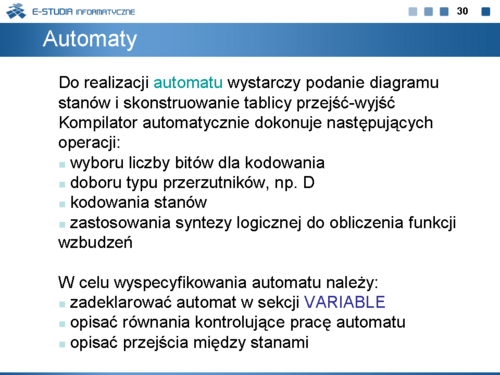

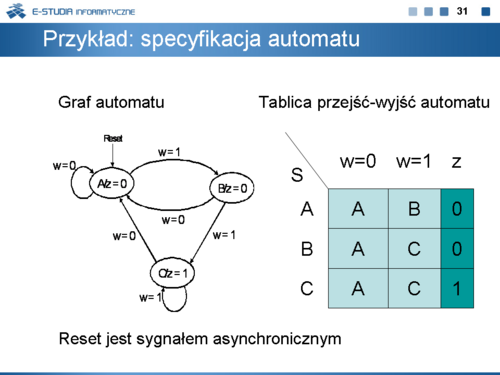

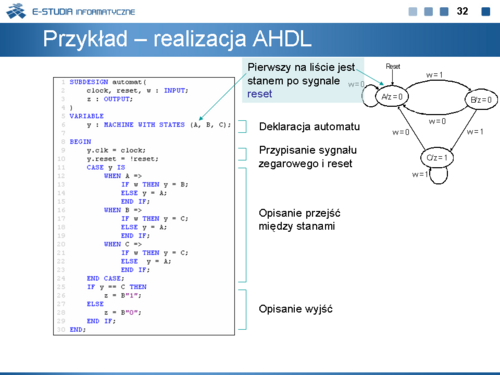

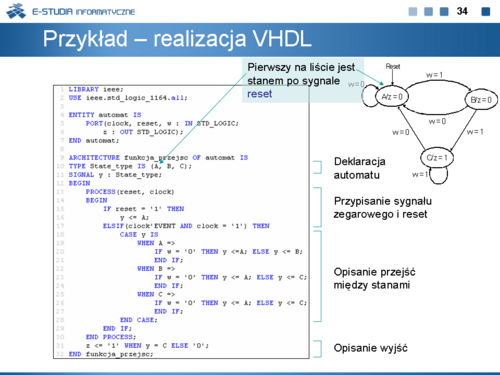

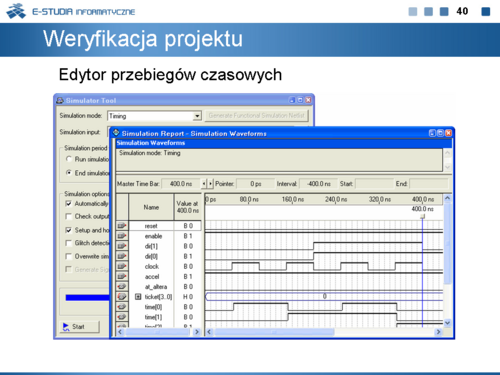

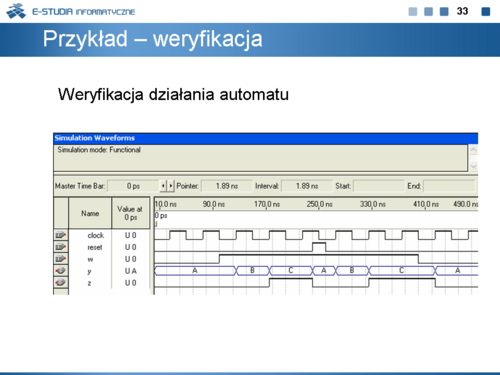

Po procesie kompilacji działanie automatu można zaobserwować na wykresach czasowych symulatora. |

|

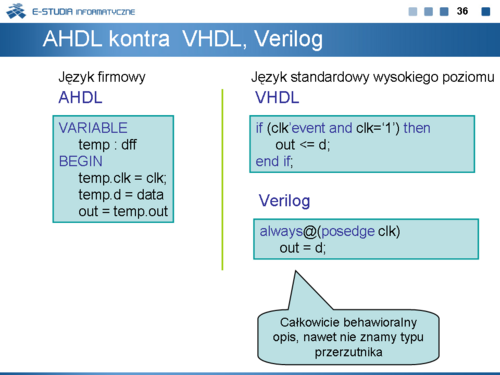

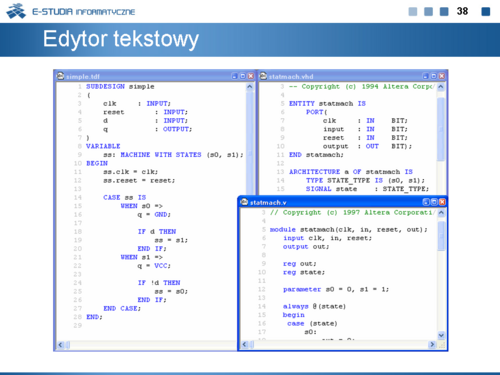

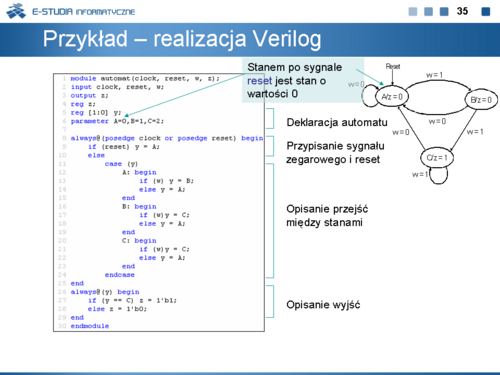

W języku Verilog deklaracja automatu jest prostsza, ale brak informacji dotyczącej przerzutników jest również charakterystyczny. |

|

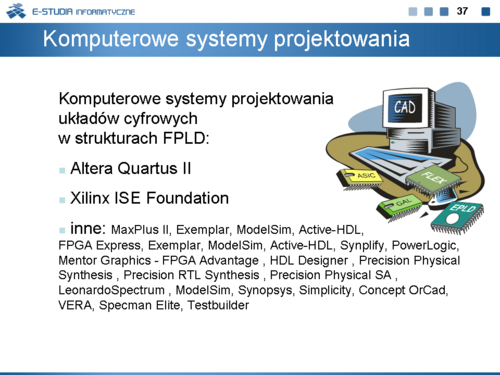

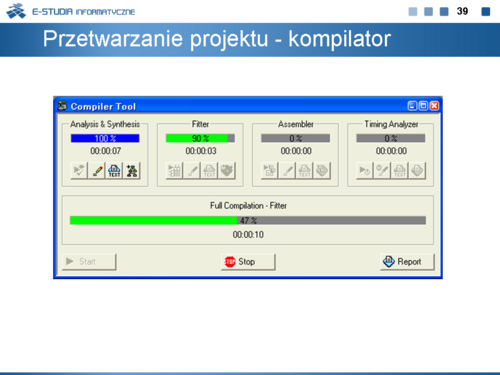

system dokona kompilacji, w ramach której wykonane zostaną wszystkie czynności związane z translacją wprowadzonej specyfikacji na poziom logiczny oraz odwzorowaniem technologicznym. |