Architektura Komputerów/Wykład 6: Jednostka wykonawcza procesora

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

|

... |

|

... |

|

... |

|

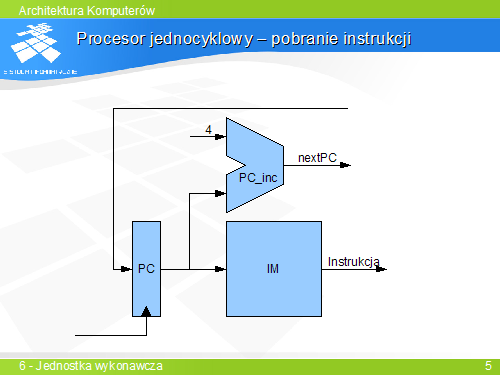

PC – licznik instrukcji PC_inc – inkrementer licznika instrukcji IM – pamięć intrukcji Inc PC – zinkrementowana wartość PC nextPC – ścieżka zawierająca następną zawartość PC |

|

... |

|

Układ sterujący jest wielowyjściowym układem kombinacyjnym. Generuje on sygnały sterujące wszystkimi częściami procesora. |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |