Sw3.6-m5-1.2-Slajd13

Systemy wbudowane(12)

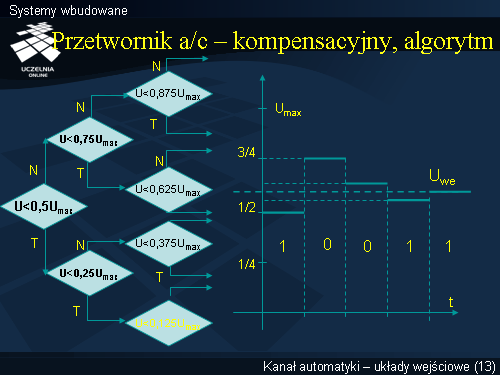

Opisaną powyżej zasadę działania przetwornika typu kompensacyjnego prezentuje powyższy algorytm. Wykres obok przedstawia sposób dochodzenia do wyniku przetwarzania. Linia przerywaną zaznaczono wartość przetwarzanego napięcia wejściowego. W pierwszym cyklu porównanie napięcia wejściowego Uwe wskazuje, że jest ono wyższe od 1 Umax . Powoduje to w konsekwencji utrzymanie załączenia najstarszego bitu przetwornika c/a i utrzymanie 1 na najstarszej pozycji w rejestrze wyjściowym (w słowie wyjściowym na najstarszej pozycji otrzymujemy 1). W kolejnym cyklu następuje załączenie n-1 bitu i wystawienie na wyjściu dodatkowo 1 Umax. Sumarycznie zatem na wejściu komparatora podawane jest napięcie równe 3 Umax. Porównanie tego napięcia z napięciem wejściowym Uwe daje odwrotny wynik – napięcie Uwe jest mniejsze od 3 Umax. Następuje zgaszenie ustawionego wcześniej n-1 bitu (w słowie wyjściowym na pozycji n-1 ustawione zostaje 0). Kolejny cykl daje analogiczny efekt – zatem znów na pozycji n-2 ustawiona zostaje wartość 0. Cykl porównań powtarzany jest n razy.

Przetwornik typu kompensacyjnego charakteryzuje się stałym czasem przetwarzania (jest to n cykli porównań plus cykl startu i gotowości do odczytania wyniku) niezależnym od wartości przetwarzanego napięcia wejściowego. Niezmiernie istotnym warunkiem poprawnej przetwornika jest utrzymanie stałej wartości napięcia wejściowego w czasie przetwarzania.

Przedstawiony przykład przetwornika w wersji najprostszej może być wyposażony w rozbudowany układ komparatorów, pozwalający na zmniejszenie liczby cykli niezbędnych do uzyskania wyniku.