Sw3.6-l1-1.2-Slajd3

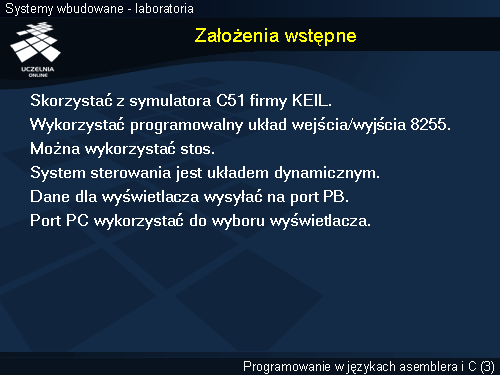

Założenia wstępne

Do napisania i przetestowania programu należy użyć symulatora C51. Należy wykorzystać wiadomości na temat programowalnego układu wejścia/wyjścia równoległego 8255. Układ 8255 posiada 8-bitowe porty PA i PB., które mogą być ustawiane jako wejścia lub jako wyjścia. Natomiast port PC podzielony jest na dwie 4-bitowe części, które można oddzielnie programować jako wejście lub jako wyjście. Sygnał RESET zeruje wszystkie rejestry układu oraz porty, dodatkowo ustawiając je jako wyjścia. Sygnałami A0 i A1 wybiera się port lub rejestr sterujący do odczytu lub zapisu danych. W trybie 1 i 2 poszczególne bity PC mogą być ustawiane lub zerowane poprzez rejestr zerujący. Jest to wykorzystywane w celu programowego blokowania i odblokowywania żądań przerwań. Układ 8255 może pracować w 3 trybach. W trybie 0 każdy z portów może pracować jako wejście lub wyjście proste. W trybie 1 Porty PA i PB mogą pracować jako wejście lub wyjście z potwierdzeniem, a port PC jako port sterujący. W ostatnim z trybów Pa pracuje jako port z możliwością transmisji dwukierunkowej z potwierdzeniem, PB w trybie 0 lub 1, a port PC jako port sterujący. W zadaniu należy wybrać odpowiedni tryb pracy. Stos wykorzystać dla zapamiętania zawartości rejestrów z grupy rejestrów specjalnego przeznaczenia SFR - DPL i DPH. Rejestry DPL i DPH tworzą razem rejestr DPTR, który jest nazywany wskaźnikiem danych. Wybór portów PB i PC wynika z trybów pracy układu 8255.