Sw3.6-l9-1.2-Slajd4

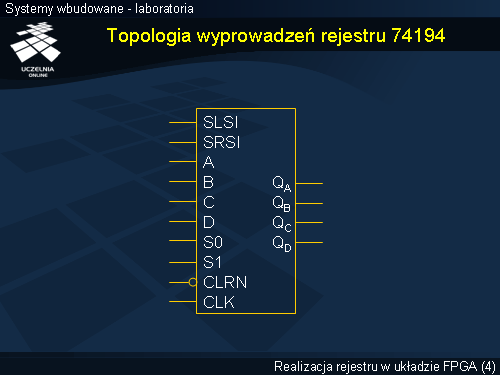

Topologia wyprowadzeń rejestru 74194

Na slajdzie została przedstawiona topologia wyprowadzeń układu 74194. Wprowadzanie równoległe jest realizowane synchronicznie z narastaniem zbocza impulsu zegarowego przez podanie czterech bitów danych na wejścia równoległe oraz ustawienie wejść rodzaju pracy S0 i S1 w stan wysoki. W czasie wprowadzania równoległego wejścia szeregowe SR i SL są zablokowane. Przesuwanie w prawo jest realizowane w momencie, gdy S0 jest w stanie wysokim, a wejście S1 jest w stanie niskim. Dane są wprowadzane wejściem SR. W trakcie przesuwania w prawo wejścia równoległe danych są zablokowane. Przesuwanie w lewo jest realizowane, gdy S0 jest w stanie niskim, a wejście S1 w stanie wysokim. Dane są wprowadzane wejściem SL. W czasie przesuwania w lewo wejścia równoległe są zablokowane. Blokada wejścia zegarowego występuje gdy S0 i S1 sa w stanie niskim. Zmiany na wejściach trybu pracy S0 i S1 powinny występować w momencie, gdy na wejściu zegarowym podany jest stan wysoki.