Architektura Komputerów/Wykład 1: Teoria: Różnice pomiędzy wersjami

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

Nie podano opisu zmian |

Nie podano opisu zmian |

||

| Linia 62: | Linia 62: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S10.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S10.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Komputer sterowany przepływem danych nie ma jawnych instrukcji. Operuje on na tzw. „toknach”, czyli obiektach złożonych z danych i opisujących je znaczników – metek. | ||

Metka zastępuje instrukcję. Na podstawie metki procesor sterowany przepływem danych przekształca cały token- zarówno dane jak i metkę, tworząc nowy token. | |||

O ile maszyny dataflow nie są współcześnie konstruowane, to samo podejście dtaflow jest używane do opisu procesów informacyjnych. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 74: | Linia 78: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S12.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S12.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Taksonomia Skillicorna jest zbudowany całkowicie odmiennie od taksonomii Flynna. Zakłada ona, że każda architektura stanowi połączenie pewnej liczby składników. W ten sposób taksonomia syntetyzuje architekturę, zamiast ją klasyfikować. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 80: | Linia 84: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S13.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S13.png]] | ||

|valign="top"| | |valign="top"| | ||

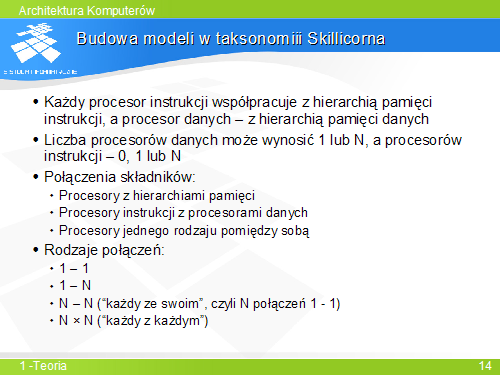

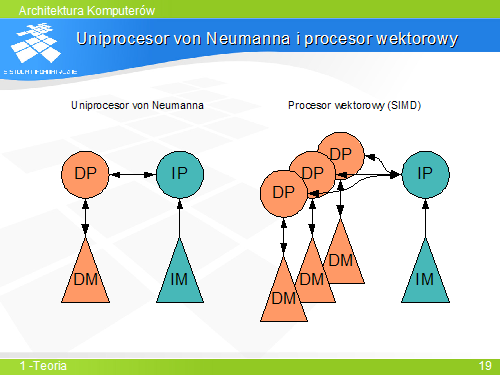

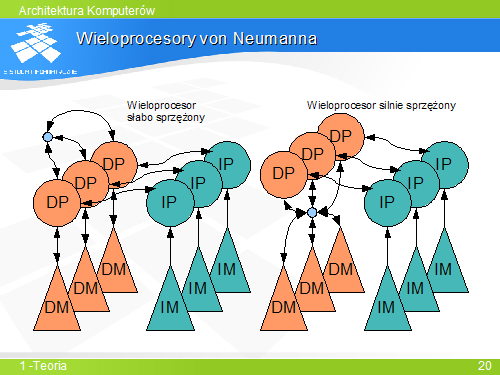

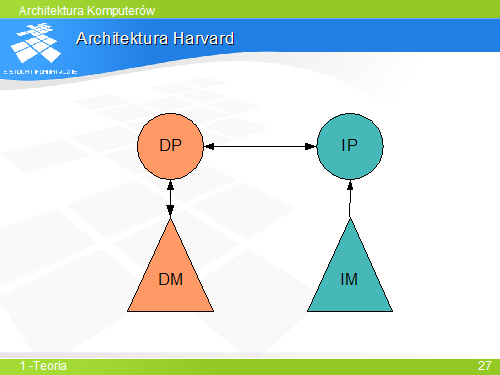

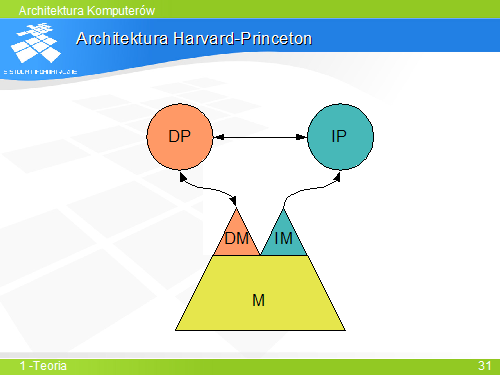

... | Taksonomia Skillicorna posługuje się abstrakcyjnymi składnikami architektury. Procesory instrukcji pobierają instrukcje z hierarchii pamięci instrukcji i przekazują je procesorom danych do wykonania. Procesory danych wykonują operacje na danych pobieranych z hierarchii pamięci danych i zapisują wyniki tych operacji z powrotem do hierarchii pamięci. Same procesory danych nie zawierają żadnych elementów pamiętających. | ||

W modelach architektur przyjmuje się, że liczba hierarchii pamięci jest równa liczbie procesorów danego typu. Oznacza to, że model architektury ze wspólną hierarchią pamięci dla kilku procesorów jest przedstawiany jako model z kilkoma hierarchiami pamięci i możliwością dostępu każdego procesora do każdej hierarchii pamięci. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

Wersja z 17:39, 4 paź 2006

|

... |

|

... |

|

... |

|

... |

|

... |

|

Rysunek przedstawia oryginalną tabelę taksonomii Flynna. Są w niej umieszczone cztery klasy architektur komputerowych. |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |