SOP wyk nr 11-Slajd14: Różnice pomiędzy wersjami

Nie podano opisu zmian |

Nie podano opisu zmian |

||

| Linia 6: | Linia 6: | ||

W przedstawionym programie instrukcja podstawienia ''n'' := ''n'' + 1 wykonywana jest współbieżnie przez 2 wątki: A oraz B, a ''n'' jest zmienną współdzieloną przez te wątki. Innymi słowy, zmienna ''n'' znajduje się w obszarze pamięci współdzielonym przez te wątki i jest dla nich zmienną wejściowo-wyjściową. Instrukcja podstawienia wymaga wykonania operacji arytmetycznej, w związku z czym może być różnie przetłumaczona na kod maszynowy, czyli na sekwencję instrukcji wykonywanych atomowo. | W przedstawionym programie instrukcja podstawienia ''n'' := ''n'' + 1 wykonywana jest współbieżnie przez 2 wątki: A oraz B, a ''n'' jest zmienną współdzieloną przez te wątki. Innymi słowy, zmienna ''n'' znajduje się w obszarze pamięci współdzielonym przez te wątki i jest dla nich zmienną wejściowo-wyjściową. Instrukcja podstawienia wymaga wykonania operacji arytmetycznej, w związku z czym może być różnie przetłumaczona na kod maszynowy, czyli na sekwencję instrukcji wykonywanych atomowo. | ||

W procesorach o architekturze RISC operacje arytmetyczne wykonywane są wyłącznie na rejestrach procesora, wobec czego podstawienie takie wymaga wcześniejszego załadowania zawartości komórki pamięci, przechowującej wartość zmiennej ''n'' do odpowiedniego rejestru, dodania wartości 1 do zawartości tego rejestru, a następnie umieszczenia zmodyfikowanej wartości ponownie w pamięci pod adresem przypisanym zmiennej ''n'' . W tym celu wątek A korzysta z jakiegoś rejestru procesora, oznaczonego '' | W procesorach o architekturze RISC operacje arytmetyczne wykonywane są wyłącznie na rejestrach procesora, wobec czego podstawienie takie wymaga wcześniejszego załadowania zawartości komórki pamięci, przechowującej wartość zmiennej ''n'' do odpowiedniego rejestru, dodania wartości 1 do zawartości tego rejestru, a następnie umieszczenia zmodyfikowanej wartości ponownie w pamięci pod adresem przypisanym zmiennej ''n'' . W tym celu wątek A korzysta z jakiegoś rejestru procesora, oznaczonego ''R<sub>A</sub>'' , a wątek B z rejestru ''R<sub>B</sub>'' . W szczególności może to być ten sam rejestr, ale raz występujący w kontekście wątku A, a raz w kontekście wątku B. | ||

W procesorach o architekturze CISC powszechne są rozkazy typu ''odczyt'' '''' ''modyfikacja'' '''' ''zapis'' (ang. read-modify-write). Przykładem może być 16- lub 32-bitowa architektura intelowska z rozkazem '''inc''' , którego operand może być w pamięci. Instrukcja ta może być zatem przekładem na kod maszynowy wysokopoziomowej instrukcja podstawienia ''n'' := ''n'' + 1. | W procesorach o architekturze CISC powszechne są rozkazy typu ''odczyt'' '''' ''modyfikacja'' '''' ''zapis'' (ang. read-modify-write). Przykładem może być 16- lub 32-bitowa architektura intelowska z rozkazem '''inc''' , którego operand może być w pamięci. Instrukcja ta może być zatem przekładem na kod maszynowy wysokopoziomowej instrukcja podstawienia ''n'' := ''n'' + 1. | ||

Wersja z 10:46, 16 sie 2006

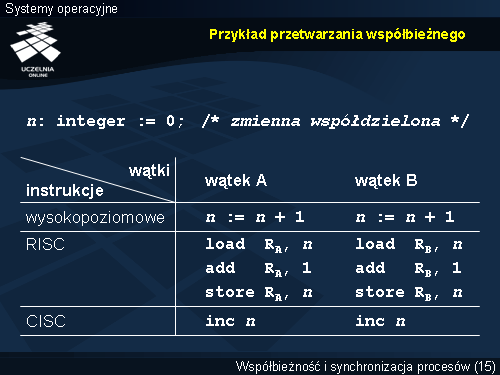

Przykład przetwarzania współbieżnego

W przedstawionym programie instrukcja podstawienia n := n + 1 wykonywana jest współbieżnie przez 2 wątki: A oraz B, a n jest zmienną współdzieloną przez te wątki. Innymi słowy, zmienna n znajduje się w obszarze pamięci współdzielonym przez te wątki i jest dla nich zmienną wejściowo-wyjściową. Instrukcja podstawienia wymaga wykonania operacji arytmetycznej, w związku z czym może być różnie przetłumaczona na kod maszynowy, czyli na sekwencję instrukcji wykonywanych atomowo.

W procesorach o architekturze RISC operacje arytmetyczne wykonywane są wyłącznie na rejestrach procesora, wobec czego podstawienie takie wymaga wcześniejszego załadowania zawartości komórki pamięci, przechowującej wartość zmiennej n do odpowiedniego rejestru, dodania wartości 1 do zawartości tego rejestru, a następnie umieszczenia zmodyfikowanej wartości ponownie w pamięci pod adresem przypisanym zmiennej n . W tym celu wątek A korzysta z jakiegoś rejestru procesora, oznaczonego RA , a wątek B z rejestru RB . W szczególności może to być ten sam rejestr, ale raz występujący w kontekście wątku A, a raz w kontekście wątku B.

W procesorach o architekturze CISC powszechne są rozkazy typu odczyt modyfikacja zapis (ang. read-modify-write). Przykładem może być 16- lub 32-bitowa architektura intelowska z rozkazem inc , którego operand może być w pamięci. Instrukcja ta może być zatem przekładem na kod maszynowy wysokopoziomowej instrukcja podstawienia n := n + 1.