PEE Moduł 10: Różnice pomiędzy wersjami

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

Nie podano opisu zmian |

Nie podano opisu zmian |

||

| Linia 349: | Linia 349: | ||

Wobec braku obciążenia czwórnika przez impedancję <math>Z_2</math> nie przepływa prąd, stąd całe napięcie wyjściowe pochodzi z impedancji poprzecznej <math>Z\,</math> (dzielnik impedancyjny). | Wobec braku obciążenia czwórnika przez impedancję <math>Z_2</math> nie przepływa prąd, stąd całe napięcie wyjściowe pochodzi z impedancji poprzecznej <math>Z\,</math> (dzielnik impedancyjny). | ||

Impedancja wejściowa czwórnika przy obciążeniu bramy wyjściowej impedancją <math>Z_0</math> na podstawie | Impedancja wejściowa czwórnika przy obciążeniu bramy wyjściowej impedancją <math>Z_0</math> na podstawie wzoru jest równa | ||

: <math>Z_{we}(s)={U_1(s) \over I_1(s)}={A_{11}+A_{12}Y_0 \over A_{21}+A_{22}Y_0}={(1+Z_1Y)+(Z_1+Z_2+Z_1Z_2Y)Y_0 \over Y+(1+Z_2Y)Y_0}</math> | : <math>Z_{we}(s)={U_1(s) \over I_1(s)}={A_{11}+A_{12}Y_0 \over A_{21}+A_{22}Y_0}={(1+Z_1Y)+(Z_1+Z_2+Z_1Z_2Y)Y_0 \over Y+(1+Z_2Y)Y_0}</math> | ||

| Linia 360: | Linia 360: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10.png]] | ||

|valign="top"|''' | |valign="top"|'''Połączenie łańcuchowe''', zwane również kaskadowym czwórników to takie połączenie , w którym zaciski wejściowe jednego czwórnika są przyłączone do zacisków wyjściowych poprzedniego. Przykład połączenia łańcuchowego dwu czwórników przedstawiony jest na rysunku obok. | ||

Łatwo jest pokazać, że macierz łańcuchowa <math>\mathbf{A}\,</math> czwórników połączonych kaskadowo jest równa iloczynowi macierzy łańcuchowych poszczególnych czwórników tworzących to połączenie | |||

: <math>\mathbf{A}=\mathbf{A}_1 \cdot \mathbf{A}_2</math> | |||

Przy większej liczbie czwórników połączonych kaskadowo macierz łańcuchowa wypadkowa jest równa iloczynowi macierzy łańcuchowych wszystkich czwórników branych w kolejności ich występowania w łańcuchu. | Przy większej liczbie czwórników połączonych kaskadowo macierz łańcuchowa wypadkowa jest równa iloczynowi macierzy łańcuchowych wszystkich czwórników branych w kolejności ich występowania w łańcuchu. | ||

: <math>A= | : <math>\mathbf{A}=\mathbf{A}_1 \mathbf{A}_2 \cdots \mathbf{A}_n</math> | ||

Należy zwrócić uwagę, że przy mnożeniu macierzy istotna jest kolejność tych macierzy, gdyż w ogólności <math> | Należy zwrócić uwagę, że przy mnożeniu macierzy istotna jest kolejność tych macierzy, gdyż w ogólności <math>\mathbf{A}_1 \cdot \mathbf{A}_2\neq \mathbf{A}_2 \cdot \mathbf{A}_1</math> | ||

|} | |||

<hr width="100%"> | |||

{| border="0" cellpadding="4" width="100%" | |||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10.png]] | |||

Dwa czwórniki są połączone szeregowo, jeśli spełnione są warunki: | |valign="top"|Dwa czwórniki są '''połączone szeregowo''', jeśli spełnione są warunki: | ||

*prąd wejściowy jednego czwórnika jest równy prądowi wejściowemu drugiego a prąd wyjściowy jednego czwórnika jest równy prądowi wyjściowemu drugiego | *prąd wejściowy jednego czwórnika jest równy prądowi wejściowemu drugiego a prąd wyjściowy jednego czwórnika jest równy prądowi wyjściowemu drugiego | ||

*napięcie wejściowe (wyjściowe) połączenia jest równe sumie napięć wejściowych (wyjściowych) każdego czwórnika. | *napięcie wejściowe (wyjściowe) połączenia jest równe sumie napięć wejściowych (wyjściowych) każdego czwórnika. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych szeregowo, spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu szeregowym czwórników macierz impedancyjna <math>Z\,</math> połączenia jest równa sumie macierzy impedancyjnych każdego czwórnika. Oznacza to, że | Łatwo jest pokazać, że w połączeniu szeregowym czwórników macierz impedancyjna <math>\mathbf{Z}\,</math> połączenia jest równa sumie macierzy impedancyjnych każdego czwórnika. Oznacza to, że | ||

: <math>Z= | : <math>\mathbf{Z}=\mathbf{Z}_1+\mathbf{Z}_2</math> | ||

Przy większej liczbie czwórników połączonych szeregowo macierz impedancyjna wypadkowa jest równa sumie macierzy impedancyjnych wszystkich czwórników występujących w połączeniu. | Przy większej liczbie czwórników połączonych szeregowo macierz impedancyjna wypadkowa jest równa sumie macierzy impedancyjnych wszystkich czwórników występujących w połączeniu. | ||

: <math>Z=\sum_{i=1}^n | : <math>\mathbf{Z}=\sum_{i=1}^n \mathbf{Z}_i</math> | ||

Kolejność sumowania macierzy impedancyjnych nie odgrywa żadnej roli. | Kolejność sumowania macierzy impedancyjnych nie odgrywa żadnej roli. | ||

|} | |} | ||

| Linia 406: | Linia 399: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd11.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd11.png]] | ||

|valign="top"|''' | |valign="top"|Dwa czwórniki są '''połączone równolegle''', jeśli spełnione są warunki: | ||

*napięcie wejściowe każdego czwórnika jest takie samo, podobnie napięcie wyjściowe | *napięcie wejściowe każdego czwórnika jest takie samo, podobnie napięcie wyjściowe | ||

*prąd wejściowy (wyjściowy) połączenia jest równy sumie prądów wejściowych (wyjściowych) każdego czwórnika. | *prąd wejściowy (wyjściowy) połączenia jest równy sumie prądów wejściowych (wyjściowych) każdego czwórnika. | ||

Ponadto w tym przypadku należy zapewnić spełnienie warunków regularności połączenia zdefiniowanych odpowiednią równością prądów | Ponadto w tym przypadku należy zapewnić spełnienie warunków regularności połączenia zdefiniowanych odpowiednią równością prądów. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych równolegle, spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu równoległym czwórników macierz admitancyjna <math>Y\,</math> połączenia jest równa sumie macierzy admitancyjnych każdego czwórnika. Oznacza to, że | Łatwo jest pokazać, że w połączeniu równoległym czwórników macierz admitancyjna <math>\mathbf{Y}\,</math> połączenia jest równa sumie macierzy admitancyjnych każdego czwórnika. Oznacza to, że | ||

: <math>Y= | : <math>\mathbf{Y}=\mathbf{Y}_1+\mathbf{Y}_2</math> | ||

Przy większej liczbie czwórników połączonych równolegle macierz admitancyjna wypadkowa jest równa sumie macierzy admitancyjnych wszystkich czwórników występujących w połączeniu. | Przy większej liczbie czwórników połączonych równolegle macierz admitancyjna wypadkowa jest równa sumie macierzy admitancyjnych wszystkich czwórników występujących w połączeniu. | ||

: <math>Y=\sum_{i=1}^n | : <math>\mathbf{Y}=\sum_{i=1}^n \mathbf{Y}_i</math> | ||

Kolejność sumowania macierzy admitancyjnych nie odgrywa żadnej roli. | Kolejność sumowania macierzy admitancyjnych nie odgrywa żadnej roli. | ||

|} | |||

<hr width="100%"> | |||

{| border="0" cellpadding="4" width="100%" | |||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10.png]] | |||

Dwa czwórniki są połączone szeregowo-równolegle, jeśli spełnione są warunki: | |valign="top"|Dwa czwórniki są '''połączone szeregowo-równolegle''', jeśli spełnione są warunki: | ||

*prąd wejściowy każdego czwórnika jest taki sam a napięcie wejściowe połączenia jest równe sumie napięć wejściowych każdego czwórnika | *prąd wejściowy każdego czwórnika jest taki sam a napięcie wejściowe połączenia jest równe sumie napięć wejściowych każdego czwórnika | ||

*prąd wyjściowy połączenia jest równy sumie prądów wyjściowych każdego czwórnika a napięcie wyjściowe obu czwórników jest takie samo. | *prąd wyjściowy połączenia jest równy sumie prądów wyjściowych każdego czwórnika a napięcie wyjściowe obu czwórników jest takie samo. | ||

Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów | Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych szeregowo-równolegle (szeregowo po stronie zacisków wejściowych i równolegle po stronie zacisków wyjściowych), spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu szeregowo-równoległym czwórników macierz hybrydowa <math>H\,</math> połączenia jest równa sumie macierzy hybrydowych <math>H\,</math> każdego czwórnika. Oznacza to, że | Łatwo jest pokazać, że w połączeniu szeregowo-równoległym czwórników macierz hybrydowa <math>H\,</math> połączenia jest równa sumie macierzy hybrydowych <math>\mathbf{H}\,</math> każdego czwórnika. Oznacza to, że | ||

: <math>H= | : <math>\mathbf{H}=\mathbf{H}_1+\mathbf{H}_2</math> | ||

Przy większej liczbie czwórników połączonych szeregowo-równolegle macierz hybrydowa <math>H\,</math>, wypadkowa dla całego połączenia jest równa sumie macierzy hybrydowych <math>H\,</math> wszystkich czwórników występujących w połączeniu. | Przy większej liczbie czwórników połączonych szeregowo-równolegle macierz hybrydowa <math>\mathbf{H}\,</math>, wypadkowa dla całego połączenia jest równa sumie macierzy hybrydowych <math>\mathbf{H}\,</math> wszystkich czwórników występujących w połączeniu. | ||

: <math>H=\sum_{i=1}^n | : <math>\mathbf{H}=\sum_{i=1}^n \mathbf{H}_i</math> | ||

Kolejność sumowania macierzy hybrydowych nie odgrywa żadnej roli. | Kolejność sumowania macierzy hybrydowych nie odgrywa żadnej roli. | ||

|} | |} | ||

| Linia 455: | Linia 447: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd12.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd12.png]] | ||

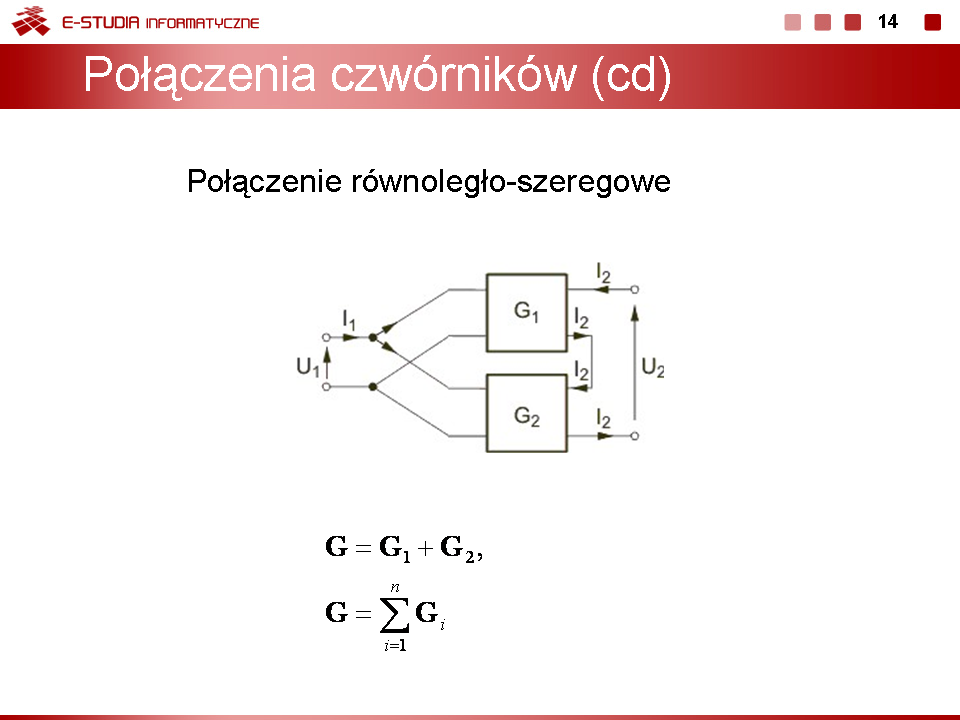

|valign="top"|''' | |valign="top"|Dwa czwórniki są '''połączone równolegle-szeregowo''', jeśli spełnione są warunki: | ||

*napięcie wejściowe każdego czwórnika jest takie samo a prąd wejściowy połączenia jest równy sumie prądów wejściowych każdego czwórnika | *napięcie wejściowe każdego czwórnika jest takie samo a prąd wejściowy połączenia jest równy sumie prądów wejściowych każdego czwórnika | ||

*prąd wyjściowy każdego czwórnika jest taki sam a napięcie wyjściowe połączenia jest równe sumie napięć wyjściowych każdego z nich. | *prąd wyjściowy każdego czwórnika jest taki sam a napięcie wyjściowe połączenia jest równe sumie napięć wyjściowych każdego z nich. | ||

Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów | Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych równolegle-szeregowo (równolegle po stronie zacisków wejściowych i szeregowo po stronie zacisków wyjściowych), spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu równolegle-szeregowym czwórników macierz hybrydowa odwrotna <math>G\,</math> połączenia jest równa sumie macierzy hybrydowych <math>G\,</math> każdego czwórnika. Oznacza to, że | Łatwo jest pokazać, że w połączeniu równolegle-szeregowym czwórników macierz hybrydowa odwrotna <math>\mathbf{G}\,</math> połączenia jest równa sumie macierzy hybrydowych <math>G\,</math> każdego czwórnika. Oznacza to, że | ||

: <math>G= | : <math>\mathbf{G}=\mathbf{G}_1+\mathbf{G}_2</math> | ||

Przy większej liczbie czwórników połączonych równolegle-szeregowo macierz hybrydowa odwrotna <math>G\,</math>, wypadkowa dla całego połączenia jest równa sumie macierzy hybrydowych <math>G\,</math> wszystkich czwórników występujących w połączeniu. | Przy większej liczbie czwórników połączonych równolegle-szeregowo macierz hybrydowa odwrotna <math>\mathbf{G}\,</math>, wypadkowa dla całego połączenia jest równa sumie macierzy hybrydowych <math>\mathbf{G}\,</math> wszystkich czwórników występujących w połączeniu. | ||

: <math>G=\sum_{i=1}^n | : <math>\mathbf{G}=\sum_{i=1}^n \mathbf{G}_i</math> | ||

Kolejność sumowania macierzy nie odgrywa żadnej roli. | Kolejność sumowania macierzy nie odgrywa żadnej roli. | ||

|} | |} | ||

| Linia 482: | Linia 471: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd13.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd13.png]] | ||

|valign="top"| | |valign="top"|'''Żyrator''' | ||

'''Żyrator''' | |||

Żyrator jest czwórnikiem opisanym następującą macierzą łańcuchową | Żyrator jest czwórnikiem opisanym następującą macierzą łańcuchową | ||

Wersja z 13:31, 25 sie 2006

|

Wykład10. Czwórniki |

Zadanie 10.1

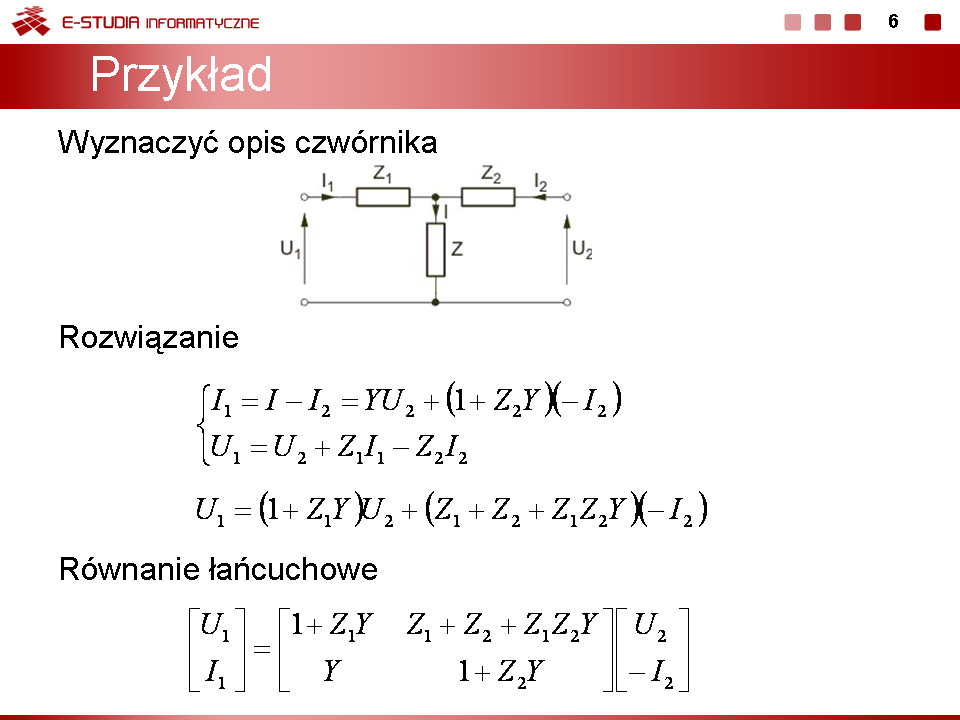

Wyznaczyć macierzowy opis czwórnikowy czwórnika typu o strukturze podanej na rysunku poniżej.

Rozwiązanie

Układ równań Kirchhoffa opisujących obwód

Równania czwórnikowe

Macierz admitancyjna

Zadanie 10.2

Wyznaczyć macierz łańcuchową czwórnika odpowiadającego obwodowi z rysunku poniżej. Określić na tej podstawie transmitancję napięciową układu.

Rozwiązanie

Z równań Kirchhoffa dla obwodu otrzymuje się

Opis łańcuchowy czwórnika

Transmitancja napięciowa określana przy założeniu jest równa