SOP wyk nr 4-Slajd41: Różnice pomiędzy wersjami

Nie podano opisu zmian |

Nie podano opisu zmian |

||

| Linia 4: | Linia 4: | ||

Przedstawiony wcześniej przykładowy podział 32-bitowego adresu logicznego na 10-bitowe przesunięcie oraz 22 bitowy numer strony oznaczałby, że potencjalnie może być potrzebnym | Przedstawiony wcześniej przykładowy podział 32-bitowego adresu logicznego na 10-bitowe przesunięcie oraz 22 bitowy numer strony oznaczałby, że potencjalnie może być potrzebnym 2<sup>22</sup> wpisów w tablicy stron. Zakładając, że każdy wpis wymaga 32 bitów (4 bajtów), na tablicę stron potrzebny byłby ciągły obszar pamięci fizycznej o rozmiarze 2<sup>24</sup> = 16 MB. Znalezienie tak dużego ciągłego obszaru może być kłopotliwe, a rozwiązaniem problemu może być zastosowanie podejścia wielopoziomowego, zwanego również hierarchicznym. W podejściu dwupoziomowym w adresie logicznym wyodrębnia się 3 zakresy bitów: | ||

* numer pozycji w zewnętrznej tablicy stron, opisującej ramkę z wewnętrzną tablicą stron, | * numer pozycji w zewnętrznej tablicy stron, opisującej ramkę z wewnętrzną tablicą stron, | ||

* numer pozycji w wewnętrznej tablicy stron, opisujący ramkę z fragmentem (stroną) obrazu procesu, | * numer pozycji w wewnętrznej tablicy stron, opisujący ramkę z fragmentem (stroną) obrazu procesu, | ||

Wersja z 08:38, 16 sie 2006

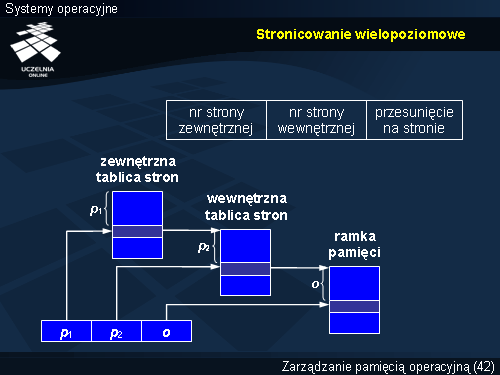

Stronicowanie wielopoziomowe

Przedstawiony wcześniej przykładowy podział 32-bitowego adresu logicznego na 10-bitowe przesunięcie oraz 22 bitowy numer strony oznaczałby, że potencjalnie może być potrzebnym 222 wpisów w tablicy stron. Zakładając, że każdy wpis wymaga 32 bitów (4 bajtów), na tablicę stron potrzebny byłby ciągły obszar pamięci fizycznej o rozmiarze 224 = 16 MB. Znalezienie tak dużego ciągłego obszaru może być kłopotliwe, a rozwiązaniem problemu może być zastosowanie podejścia wielopoziomowego, zwanego również hierarchicznym. W podejściu dwupoziomowym w adresie logicznym wyodrębnia się 3 zakresy bitów:

- numer pozycji w zewnętrznej tablicy stron, opisującej ramkę z wewnętrzną tablicą stron,

- numer pozycji w wewnętrznej tablicy stron, opisujący ramkę z fragmentem (stroną) obrazu procesu,

- przesunięcie wewnątrz ramki z fragmentem obrazu procesu.

Podejście takie zastosowano między innymi w architekturze Intel IA-32. Zewnętrzną tablicę stron określa się jako katalog stron , a wewnętrzną po prostu jako tablicę stron. Na identyfikację pozycji w katalogu stron oraz w tablicy stron przeznaczone jest po 10 bitów z 32-bitowego adresu. Na przesunięcie na stronie pozostaje zatem 12 bitów, co oznacza, że rozmiar strony wynosi 4 KB. W architekturze

Sparc zastosowano nawet podeście trzypoziomowe.