Architektura Komputerów/Wykład 6: Jednostka wykonawcza procesora: Różnice pomiędzy wersjami

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

Nie podano opisu zmian |

Nie podano opisu zmian |

||

| (Nie pokazano 4 pośrednich wersji utworzonych przez tego samego użytkownika) | |||

| Linia 1: | Linia 1: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S01.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 8: | Linia 8: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S02.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 14: | Linia 14: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S03.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 20: | Linia 20: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S04.png]] | ||

|valign="top"| | |valign="top"| | ||

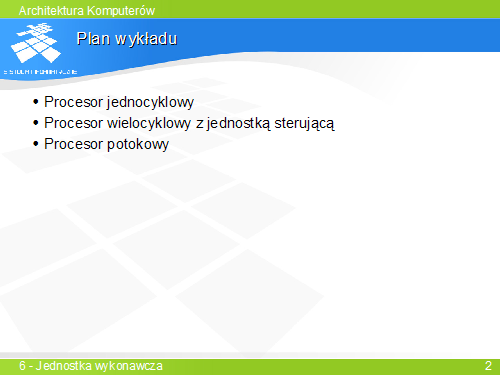

... | Modelowy procesor ma możliwość wykonywania instrukcji MIPS w dwóch spośród trzech formatów – R oraz I. W obu formatach występują pola głównego kodu operacyjnego i dwa numery rejestrów. Pozostała część słowa instrukcji jest różna dla obu formatów. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S05.png]] | ||

|valign="top"| | |valign="top"| | ||

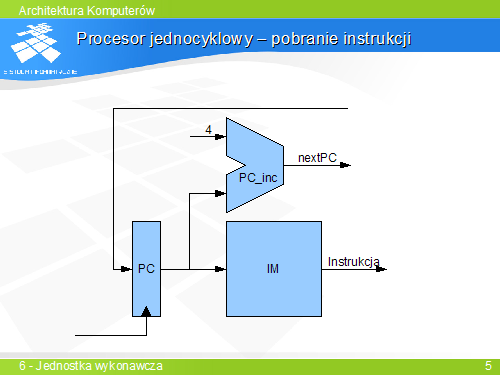

PC – licznik instrukcji | |||

PC_inc – inkrementer licznika instrukcji | |||

IM – pamięć intrukcji | |||

Inc PC – zinkrementowana wartość PC | |||

nextPC – ścieżka zawierająca następną zawartość PC | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S06.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 38: | Linia 46: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S07.png]] | ||

|valign="top"| | |valign="top"| | ||

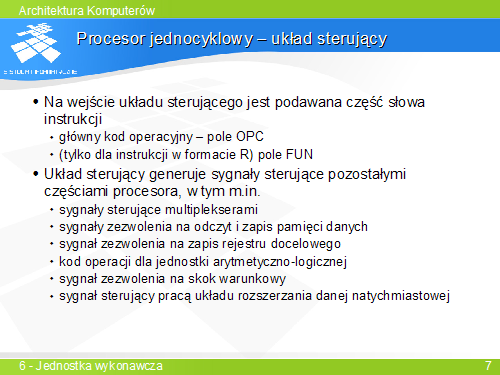

. | Układ sterujący jest wielowyjściowym układem kombinacyjnym. Generuje on sygnały sterujące wszystkimi częściami procesora. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S08.png]] | ||

|valign="top"| | |valign="top"| | ||

... | OPC, FUN, Rs, Rt, Rd, offset – pola obrazu binarnego instrukcji. | ||

RdA1, RdA2 – adresy odczytu zestawu rejestrów (numery odczytywanych rejestrów). | |||

WrA – Numer rejestru zapisywanego. | |||

WrD – dane zapisywane do rejstru. | |||

RdD1, RdD2 – dane odczytywane z rejestrów. | |||

Mux_ALU – multiplekser wyboru drugiego argumentu źródłowego. | |||

BrOffset – przemieszczenie skoku. | |||

StoreData - dane zapisywane do pamięci. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S09.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 56: | Linia 78: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S10.png]] | ||

|valign="top"| | |valign="top"| | ||

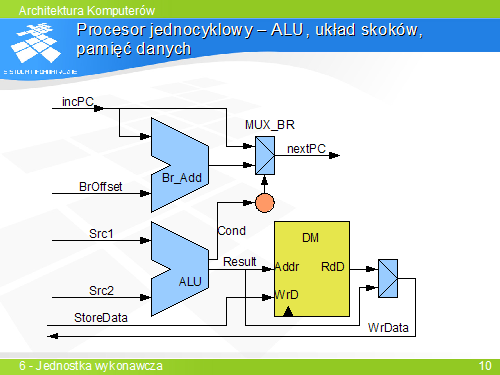

... | Br_Add – sumator adresów docelowych skoków. | ||

MUX_BR – multiplekser skoków warunkowych. | |||

ALU – jednostka arytmetyczno – logiczna. | |||

Result – wynik operacji. | |||

Cond – warunek skoku. | |||

DM – pamięć danych. | |||

WrData – dane zapisywane do rejestru. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S11.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 68: | Linia 102: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S12.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

|} | |} | ||

<!-- | |||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S13.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

|} | |} | ||

--> | |||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S14.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 86: | Linia 122: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S15.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 92: | Linia 128: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S16.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 98: | Linia 134: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S17.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 104: | Linia 140: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S18.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 110: | Linia 146: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S19.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 116: | Linia 152: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S20.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 122: | Linia 158: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S21.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 128: | Linia 164: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S22.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 134: | Linia 170: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S23.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 140: | Linia 176: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S24.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 146: | Linia 182: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S25.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 152: | Linia 188: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S26.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 158: | Linia 194: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S27.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 164: | Linia 200: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S28.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 170: | Linia 206: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S29.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 176: | Linia 212: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S30.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 182: | Linia 218: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S31.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

|} | |} | ||

<!-- | |||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S32.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

|} | |} | ||

--> | |||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S33.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 200: | Linia 238: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S34.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 206: | Linia 244: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S35.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 212: | Linia 250: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S36.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

| Linia 218: | Linia 256: | ||

<hr width="100%"> | <hr width="100%"> | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika: | |valign="top" width="500px"|[[Grafika:ASK_M06_S37.png]] | ||

|valign="top"| | |valign="top"| | ||

... | ... | ||

|} | |} | ||

Aktualna wersja na dzień 19:47, 24 paź 2006

|

... |

|

... |

|

... |

|

PC – licznik instrukcji PC_inc – inkrementer licznika instrukcji IM – pamięć intrukcji Inc PC – zinkrementowana wartość PC nextPC – ścieżka zawierająca następną zawartość PC |

|

... |

|

Układ sterujący jest wielowyjściowym układem kombinacyjnym. Generuje on sygnały sterujące wszystkimi częściami procesora. |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |