Architektura Komputerów/Wykład 1: Teoria: Różnice pomiędzy wersjami

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

Nie podano opisu zmian |

Nie podano opisu zmian |

||

| (Nie pokazano 3 pośrednich wersji utworzonych przez tego samego użytkownika) | |||

| Linia 34: | Linia 34: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S06.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S06.png]] | ||

|valign="top"| | |valign="top"| | ||

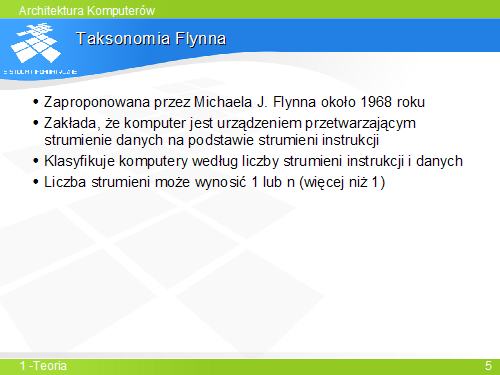

. | Rysunek przedstawia oryginalną tabelę taksonomii Flynna. Są w niej umieszczone cztery klasy architektur komputerowych. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 40: | Linia 40: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S07.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S07.png]] | ||

|valign="top"| | |valign="top"| | ||

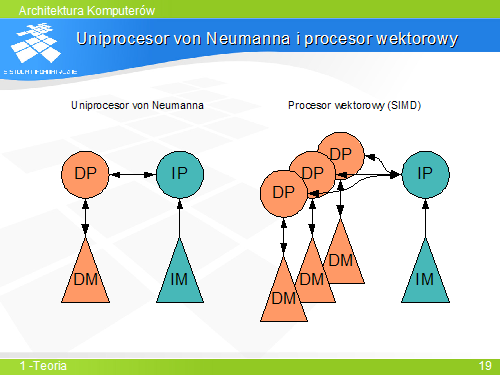

... | Przykładem architektury klasy SISD jest najbardziej rozpowszechniona architektura – uniprocesor von Neumanna, opisany w dalszym ciągu wykładu. | ||

Klasa MISD jest dość problematyczna – trudno wskazać wzorcowego reprezentanta tego typu. Można przyjąć, że założenia MISD w pewnym sensie realizują maszyny potokowe, np. procesory graficzne. | |||

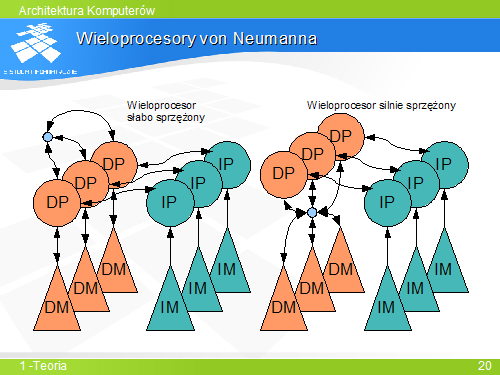

Do klasy MIMD należą tzw. wieloprocesory lub wielokomputery von Neumanna, czyli maszyny złożone z wielu połączonych uniprocesorów von Neumanna. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 46: | Linia 50: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S08.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S08.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Tabelę Flynna można rozszerzyć o dodatkowy wiersz i kolumnę, odpowiadające zerowej liczbie strumieni instrukcji i danych. Urządzenie bez strumieni danych nie jest komputerem – w tej części tabeli można by umieścić niektóre automaty. Znacznie bardziej interesujący jest wiersz odpowiadający architekturom bez strumieni instrukcji. Są to tzw. komputery sterowane przepływem danych. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 58: | Linia 62: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S10.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S10.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Komputer sterowany przepływem danych nie ma jawnych instrukcji. Operuje on na tzw. „tokenach”, czyli obiektach złożonych z danych i opisujących je znaczników – metek. | ||

Metka zastępuje instrukcję. Na podstawie metki procesor sterowany przepływem danych przekształca cały token- zarówno dane jak i metkę, tworząc nowy token. | |||

O ile maszyny dataflow nie są współcześnie konstruowane, to samo podejście dtaflow jest używane do opisu procesów informacyjnych. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 70: | Linia 78: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S12.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S12.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Taksonomia Skillicorna jest zbudowany całkowicie odmiennie od taksonomii Flynna. Zakłada ona, że każda architektura stanowi połączenie pewnej liczby składników. W ten sposób taksonomia syntetyzuje architekturę, zamiast ją klasyfikować. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 76: | Linia 84: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S13.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S13.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Taksonomia Skillicorna posługuje się abstrakcyjnymi składnikami architektury. Procesory instrukcji pobierają instrukcje z hierarchii pamięci instrukcji i przekazują je procesorom danych do wykonania. Procesory danych wykonują operacje na danych pobieranych z hierarchii pamięci danych i zapisują wyniki tych operacji z powrotem do hierarchii pamięci. Same procesory danych nie zawierają żadnych elementów pamiętających. | ||

W modelach architektur przyjmuje się, że liczba hierarchii pamięci jest równa liczbie procesorów danego typu. Oznacza to, że model architektury ze wspólną hierarchią pamięci dla kilku procesorów jest przedstawiany jako model z kilkoma hierarchiami pamięci i możliwością dostępu każdego procesora do każdej hierarchii pamięci. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 82: | Linia 92: | ||

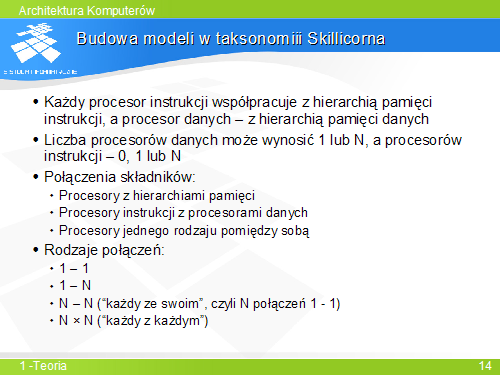

|valign="top" width="500px"|[[Grafika:ASK_M1_S14.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S14.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Tworząc modele w taksonomii Skillicorna przyjmuje się kilak założeń. Liczba hierarchii pamięci jest równa liczbie procesorów. Komputer musi zawierać przynajmniej jeden procesor danych. Dozwolone są połączenia pomiędzy procesorami i hierarchiami pamięci tego samego rodzaju (kodu albo danych) oraz połączenia pomiędzy procesorami. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 88: | Linia 98: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S15.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S15.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Rysunek przedstawia prosty model w taksonomii Skillicorna (jest to model uniprocesora von Neumanna). Procesory są oznaczone symbolicznie kołami, a hierarchie pamięci – trójkątami. Strzałki reprezentują połączenia i kierunki przesyłania informacji. | ||

Strzałki pionowe z prawej strony procesorów i hierarchii pamięci reprezentują żądania dostępów, a strzałki po prawej stronie – przepływ instrukcji i danych. | |||

Na kolejnych rysunkach podwójne strzałki zostaną zastąpione pojedynczymi, reprezentującymi kierunki przepływu danych i instrukcji, z pominięciem żądań dostępu. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 94: | Linia 107: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S16.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S16.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Procesor instrukcji przesyła do hierarchii pamięci instrukcji żądanie pobrania instrukcji. W odpowiedzi otrzymuje instrukcje. instrukcje przesyłane są po zdekodowaniu do procesora danych, który wykonuje operacje na danych. | ||

Procesor danych przesyła do hierarchii pamięci żądania operacji odczytu i zapisu. Dane pomiędzy procesorem danych i hierarchią pamięci danych przesyłane są w dwóch kierunkach (strzałka po prawej stronie). | |||

Procesor danych przesyła do procesora instrukcji informacje o stanie przetwarzania, umożliwiające procesorowi instrukcji decydowanie o dalszym przebiegu wykonania programu w zależności od wyników przetwarzania danych. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 100: | Linia 117: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S17.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S17.png]] | ||

|valign="top"| | |valign="top"| | ||

Spośród około 30 możliwych topologicznie modeli tylko 7 reprezentuje realizowalne architektury komputerów. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 124: | Linia 141: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S21.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S21.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Taksonomia Skillicorna posługuje się pojęciem hierarchii pamięci w miejsce dużo bardziej popularnego pojęcia pamięci. Słowo „hierarchia” dobrze oddaje budowę pamięci współczesnego komputera, w którym znajduje się kilka bloków funkcjonalnych służących do przechowywania programów i danych. | ||

Idealny komputer powinien mieć jak największą i jak najszybszą pamięć. Pojemność pamięci wpływa na jej fizyczne rozmiary, a te – na czas dostępu. Nie można więc zbudować dowolnie dużej i jednocześnie szybkiej pamięci. | |||

Problem ten rozwiązuje się przez wyodrębnienie wielu warstw o zróżnicowanej pojemności i szybkości, tworzących razem hierarchię pamięci. Kolejne warstwa w miarę oddalania się od procesora mają coraz większe pojemności i coraz dłuższe czasy dostępu. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 130: | Linia 151: | ||

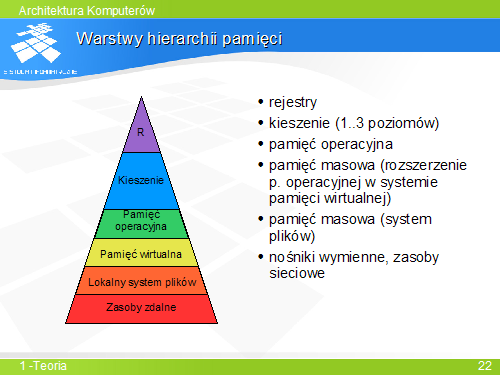

|valign="top" width="500px"|[[Grafika:ASK_M1_S22.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S22.png]] | ||

|valign="top"| | |valign="top"| | ||

... | Hierarchia pamięci współczesnego komputera, z punktu widzenia konstrukcji komputera, składa się z czterech warstw. | ||

Rejestry fizycznie znajdują się wewnątrz procesora, dzięki czemu dostęp do nich jest bardzo szybki. | |||

Kieszenie, wprowadzone po raz pierwszy około 1968 roku, zapewniają buforowania danych pomiędzy procesorem i pamięcią operacyjną w celu przyspieszenie dostępu do pamięci. | |||

Warstwa pamięci wirtualnej, powstała również około 1968 roku, zapewnia rozszerzenie pamięci operacyjnej. | |||

Z punktu widzenia użytkownika do hierarchii pamięci należy zaliczyć wszelkie zasoby służące przechowywaniu danych. Logiczne staje się więc uzupełnienie rysunku o lokalny system plików komputera oraz o zasoby zdalne, w postaci nośników wymiennych i serwerów sieciowych. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 136: | Linia 165: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S23.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S23.png]] | ||

|valign="top"| | |valign="top"| | ||

... | O ile zasada działania hierarchii pamięci dotyczy wszystkich warstw, to mechanizmy sterujące przemieszczaniem danych pomiędzy poszczególnymi warstwami są różne. | ||

O umieszczeniu danych w rejestrach decyduje programista piszący program w języku asemblerowym lub kompilator języka wysokiego poziomu. | |||

Styk warstwy kieszeni i pamięci operacyjnej jest sterowany na poziomie sprzętu. Stykiem pamięci operacyjnej i wirtualnej steruje system operacyjny przy użyciu jednostki zarządzania pamięcią. | |||

O umieszczeniu danych w pamięci wirtualnej decyduje użytkownik – otwierając plik danych lub uruchamiając program. | |||

Przemieszczaniem danych pomiędzy lokalnym systemem plików i nośnikami wymiennymi lub zasobami sieciowymi steruje użytkownik. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 142: | Linia 179: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S24.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S24.png]] | ||

|valign="top"| | |valign="top"| | ||

. | Tabela przedstawia orientacyjne parametry poszczególnych warstw hierarchii pamięci. Należy zwrócić uwagę na dużą różnicę czasów dostępu kieszeni i pamięci – czas podany dla pamięci dotyczy pojedynczego, losowego dostępu do pamięci dynamicznej typu DDR. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 148: | Linia 185: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S25.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S25.png]] | ||

|valign="top"| | |valign="top"| | ||

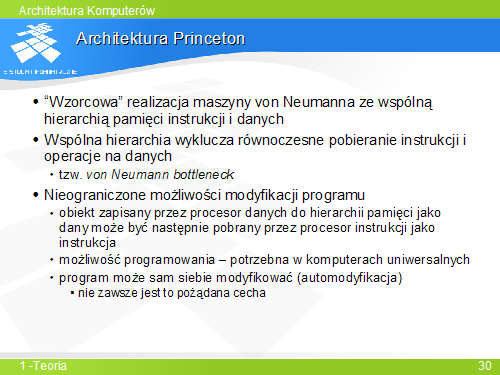

... | Architektura von Neumanna jest określona przez zestaw cech. Model maszyny von Neumanna wprowadza specyficzny mechanizm dostępu do pamięci – poprzez adres. | ||

Z takiej organizacji pamięci i z faktu przechowywania w niej programu wynika z kolei obecność rejestru licznika instrukcji. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 154: | Linia 193: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S26.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S26.png]] | ||

|valign="top"| | |valign="top"| | ||

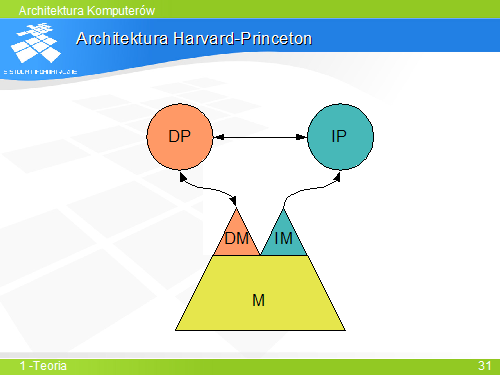

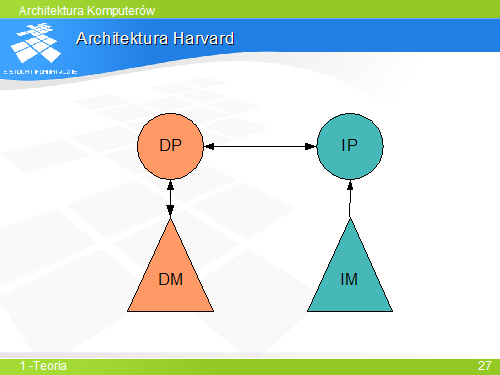

... | Dwa warianty architektury von Neumanna różnią się sposobem przechowywania instrukcji i danych. Architektura Harvard jest niekiedy uważana za architekturę nie spełniającą postulatów von Neumanna wobec faktu oddzielnego przechowywania instrukcji i danych. | ||

Kolejne rysunki posługują się symbolami zapożyczonymi z taksonomii Skillicorna w sposób sprzeczny z zasadami budowy modeli wprowadzonymi przez tę taksonomię. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 184: | Linia 225: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S31.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S31.png]] | ||

|valign="top"| | |valign="top"| | ||

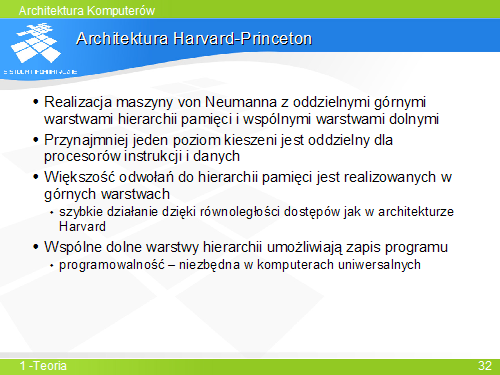

. | Hierarchia pamięci w architekturze Harvard-Princeton charakteryzuje się częściowym rozdzieleniem hierarchii pamięci. Co najmniej jeden poziom kieszeni jest oddzielny dla hierarchii pamięci instrukcji i danych. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 190: | Linia 231: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S32.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S32.png]] | ||

|valign="top"| | |valign="top"| | ||

. | Architektura Harvard-Princeton łączy zalety architektury Harvard (wydajność) i Princeton (programowalność). Programowalność nie jest tu jednak dokładnie taka sama, jak w architekturze Princeton. | ||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

| Linia 196: | Linia 237: | ||

|valign="top" width="500px"|[[Grafika:ASK_M1_S33.png]] | |valign="top" width="500px"|[[Grafika:ASK_M1_S33.png]] | ||

|valign="top"| | |valign="top"| | ||

Wszystkie produkowane współcześnie procesory do komputerów uniwersalnych mają architekturę Harvard-Princeton, z rozdzielonymi kieszeniami kodu i danych. | |||

|} | |} | ||

Aktualna wersja na dzień 21:49, 5 paź 2006

|

... |

|

... |

|

... |

|

... |

|

... |

|

Rysunek przedstawia oryginalną tabelę taksonomii Flynna. Są w niej umieszczone cztery klasy architektur komputerowych. |

|

... |

|

... |

|

Spośród około 30 możliwych topologicznie modeli tylko 7 reprezentuje realizowalne architektury komputerów. |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

... |

|

Architektura Harvard-Princeton łączy zalety architektury Harvard (wydajność) i Princeton (programowalność). Programowalność nie jest tu jednak dokładnie taka sama, jak w architekturze Princeton. |

|

Wszystkie produkowane współcześnie procesory do komputerów uniwersalnych mają architekturę Harvard-Princeton, z rozdzielonymi kieszeniami kodu i danych. |