SO-1st-2.3-w11.tresc-1.0-Slajd32: Różnice pomiędzy wersjami

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

Nie podano opisu zmian |

Nie podano opisu zmian |

||

| (Nie pokazano 1 pośredniej wersji utworzonej przez tego samego użytkownika) | |||

| Linia 4: | Linia 4: | ||

Atomowo wykonywana operacja '''exchange''' polega na zamianie wartości dwóch zmiennych logicznych. Podobnie, jak w przypadku '''test&set''' , w systemie jednoprocesorowym efekt atomowości operacji można uzyskać poprzez zablokowanie przerwań na czas jej wykonywania. | Atomowo wykonywana operacja '''exchange''' polega na zamianie wartości dwóch zmiennych logicznych. Podobnie, jak w przypadku '''test & set''', w systemie jednoprocesorowym efekt atomowości operacji można uzyskać poprzez zablokowanie przerwań na czas jej wykonywania. | ||

W architekturze IA-32 (Intel) operacja '''exchange''' realizowana jest na poziomie maszynowym przez rozkaz: '''xchg''' , dotyczy jednak nie bitów a zawartości całych rejestrów. Pewnym ograniczeniem jest fakt, że jeden z operandów musi być w rejestrze procesora, ale nie przeszkadza to np. w zastosowaniu tego. rozkazu do rozwiązania problemu wzajemnego wykluczania. Jeśli któryś z operandów rozkazu '''xchg''' jest w pamięci, następuje blokada magistrali niezależnie od użycia prefiksu lock. | W architekturze IA-32 (Intel) operacja '''exchange''' realizowana jest na poziomie maszynowym przez rozkaz: '''xchg''' , dotyczy jednak nie bitów a zawartości całych rejestrów. Pewnym ograniczeniem jest fakt, że jeden z operandów musi być w rejestrze procesora, ale nie przeszkadza to np. w zastosowaniu tego. rozkazu do rozwiązania problemu wzajemnego wykluczania. Jeśli któryś z operandów rozkazu '''xchg''' jest w pamięci, następuje blokada magistrali niezależnie od użycia prefiksu lock. | ||

Aktualna wersja na dzień 13:46, 22 wrz 2006

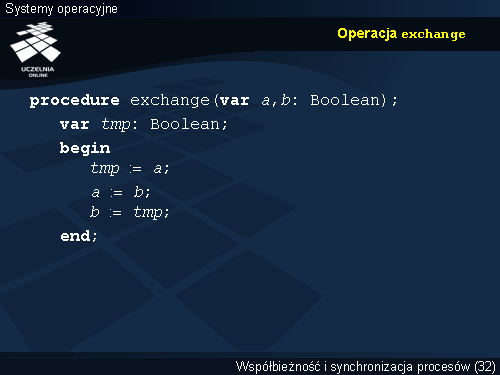

Operacja exchange

Atomowo wykonywana operacja exchange polega na zamianie wartości dwóch zmiennych logicznych. Podobnie, jak w przypadku test & set, w systemie jednoprocesorowym efekt atomowości operacji można uzyskać poprzez zablokowanie przerwań na czas jej wykonywania.

W architekturze IA-32 (Intel) operacja exchange realizowana jest na poziomie maszynowym przez rozkaz: xchg , dotyczy jednak nie bitów a zawartości całych rejestrów. Pewnym ograniczeniem jest fakt, że jeden z operandów musi być w rejestrze procesora, ale nie przeszkadza to np. w zastosowaniu tego. rozkazu do rozwiązania problemu wzajemnego wykluczania. Jeśli któryś z operandów rozkazu xchg jest w pamięci, następuje blokada magistrali niezależnie od użycia prefiksu lock.