PEE Moduł 10: Różnice pomiędzy wersjami

Z Studia Informatyczne

Przejdź do nawigacjiPrzejdź do wyszukiwania

Nie podano opisu zmian |

m Zastępowanie tekstu – „\</math>” na „\ </math>” |

||

| (Nie pokazano 10 wersji utworzonych przez 2 użytkowników) | |||

| Linia 1: | Linia 1: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd1.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd1.png|500px]] | ||

|valign="top"| | |valign="top"| | ||

|} | |} | ||

| Linia 7: | Linia 7: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd2.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd2.png|500px]] | ||

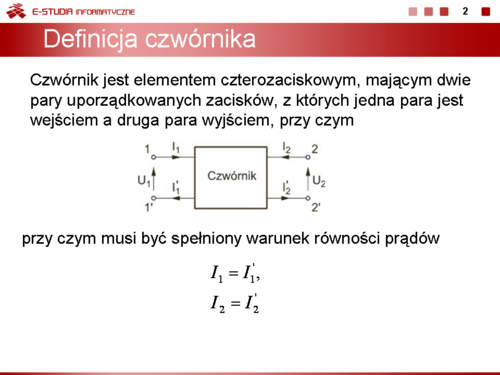

|valign="top"|'''Definicja czwórnika''' | |valign="top"|'''Definicja czwórnika''' | ||

Czwórnik jest elementem czterozaciskowym, mającym dwie pary uporządkowanych zacisków, z których jedna para jest wejściem a druga para wyjściem Oznaczenie czwórnika z zaznaczonymi zwrotami prądów i napięć końcówkowych jest przedstawione na rysunku na slajdzie | Czwórnik jest elementem czterozaciskowym, mającym dwie pary uporządkowanych zacisków, z których jedna para jest wejściem a druga para wyjściem Oznaczenie czwórnika z zaznaczonymi zwrotami prądów i napięć końcówkowych jest przedstawione na rysunku na slajdzie obok. W odniesieniu do wejścia i wyjścia czwórnika musi być spełniony warunek równości prądów: | ||

: <math>I_1=I_1^'</math><span id="wzor_10_1"></span> | : <math>I_1=I_1^'</math><span id="wzor_10_1"></span> | ||

| Linia 17: | Linia 17: | ||

jak to zaznaczono na rysunku. Sygnały prądu i napięcia po stronie wejściowej oznaczać będziemy ze wskaźnikiem 1, a po stronie wyjściowej – ze wskaźnikiem 2. Przyjmiemy umownie, że oba prądy: na wejściu i wyjściu są zwrócone do prostokąta oznaczającego czwórnik. | jak to zaznaczono na rysunku. Sygnały prądu i napięcia po stronie wejściowej oznaczać będziemy ze wskaźnikiem 1, a po stronie wyjściowej – ze wskaźnikiem 2. Przyjmiemy umownie, że oba prądy: na wejściu i wyjściu są zwrócone do prostokąta oznaczającego czwórnik. | ||

W zależności od elementów tworzących obwód, czwórnik może być liniowy (gdy wszystkie elementy obwodu są liniowe) lub nieliniowy. W dalszych rozważaniach ograniczymy się wyłącznie do czwórników liniowych. Czwórnik nazywać będziemy pasywnym, jeśli nie wytwarza energii a jedynie pobiera ją ze źródła zasilającego i przetwarza w określony sposób. Czwórnik złożony z samych elementów pasywnych R, L, C i M jest zawsze czwórnikiem pasywnym. Czwórnik pasywny jest zdolny do gromadzenia i rozpraszania energii pobranej ze źródła, może ją również oddawać na zewnątrz, jednak w dowolnej chwili czasowej <math>t\ | W zależności od elementów tworzących obwód, czwórnik może być liniowy (gdy wszystkie elementy obwodu są liniowe) lub nieliniowy. W dalszych rozważaniach ograniczymy się wyłącznie do czwórników liniowych. Czwórnik nazywać będziemy pasywnym, jeśli nie wytwarza energii a jedynie pobiera ją ze źródła zasilającego i przetwarza w określony sposób. Czwórnik złożony z samych elementów pasywnych <math>R</math>, <math>L</math>, <math>C</math> i <math>M</math> jest zawsze czwórnikiem pasywnym. Czwórnik pasywny jest zdolny do gromadzenia i rozpraszania energii pobranej ze źródła, może ją również oddawać na zewnątrz, jednak w dowolnej chwili czasowej <math>t\ </math>, energia ta nie może przewyższać energii pobranej. Czwórnik, który nie spełnia powyższych warunków jest czwórnikiem aktywnym (generatorem energii). | ||

|} | |} | ||

| Linia 24: | Linia 24: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd3.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd3.png|500px]] | ||

|valign="top"|'''Równania czwórnika''' | |valign="top"|'''Równania czwórnika''' | ||

| Linia 40: | Linia 40: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd4.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd4.png|500px]] | ||

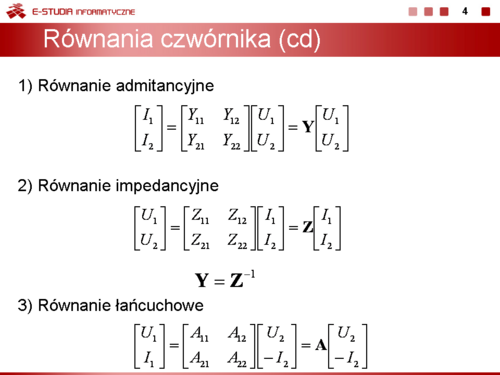

|valign="top"|'''Równanie admitancyjne''' | |valign="top"|'''Równanie admitancyjne''' | ||

| Linia 66: | Linia 66: | ||

</math> | </math> | ||

Macierz <math>\mathbf{Y}\ | Macierz <math>\mathbf{Y}\ </math>, jest nazywana macierzą admitancyjną a parametry tej macierzy mają interpretację admitancji operatorowych. | ||

| Linia 94: | Linia 94: | ||

</math> | </math> | ||

Macierz <math>\mathbf{Z}\ | Macierz <math>\mathbf{Z}\ </math>, jest nazywana macierzą impedancyjną a parametry tej macierzy mają interpretację impedancji operatorowych. Łatwo jest udowodnić, że macierze impedancyjna i admitancyjna są powiązane relacją | ||

: <math>\mathbf{Y}=\mathbf{Z}^{-1}</math> | : <math>\mathbf{Y}=\mathbf{Z}^{-1}</math> | ||

| Linia 130: | Linia 130: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd5.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd5.png|500px]] | ||

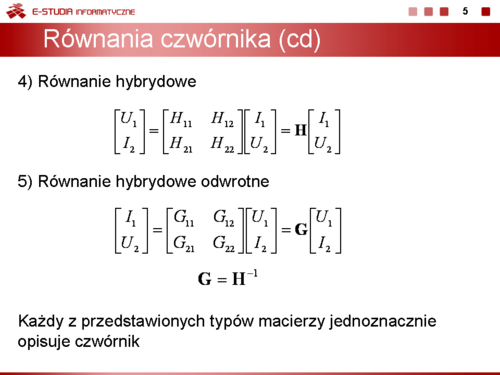

|valign="top"|'''Równania hybrydowe''' | |valign="top"|'''Równania hybrydowe''' | ||

| Linia 156: | Linia 156: | ||

</math> | </math> | ||

w której <math>\mathbf{H}\ | w której <math>\mathbf{H}\ </math>, jest '''macierzą hybrydową'''. Jak widać z opisu hybrydowego parametr <math>H_{11}</math> ma interpretację impedancji a <math>H_{22}</math> admitancji. Parametry <math>H_{12}</math> i <math>H_{21}</math> są bezwymiarowe i wyrażają stosunek odpowiednio dwu napięć i dwu prądów w obwodzie. | ||

| Linia 182: | Linia 182: | ||

</math> | </math> | ||

Stanowi on odwrotność opisu hybrydowego macierzą <math>\mathbf{H}\ | Stanowi on odwrotność opisu hybrydowego macierzą <math>\mathbf{H}\ </math>,. Obie macierze powiązane są następująca relacją | ||

: <math>\mathbf{G}=\mathbf{H}^{-1}</math> | : <math>\mathbf{G}=\mathbf{H}^{-1}</math> | ||

Duża liczba stosowanych opisów macierzowych czwórnika wynika również z faktu, że dla niektórych czwórników pewne opisy mogą nie istnieć. Najbardziej uniwersalne pod tym względem są opisy hybrydowe wykorzystujące macierz <math>\mathbf{H}\ | Duża liczba stosowanych opisów macierzowych czwórnika wynika również z faktu, że dla niektórych czwórników pewne opisy mogą nie istnieć. Najbardziej uniwersalne pod tym względem są opisy hybrydowe wykorzystujące macierz <math>\mathbf{H}\ </math>, lub <math>\mathbf{G}\ </math>,, które można otrzymać dla większości obwodów elektrycznych. | ||

|} | |} | ||

| Linia 193: | Linia 193: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd6.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd6.png|500px]] | ||

|valign="top"|Jako przykład wyznaczymy opis czwórnika przedstawionego na rysunku na slajdzie 6. Czwórnik ten nosi nazwę czwórnika typu <math>T\ | |valign="top"|Jako przykład wyznaczymy opis czwórnika przedstawionego na rysunku na slajdzie 6. Czwórnik ten nosi nazwę czwórnika typu <math>T\ </math>, i jest jedną z najpopularniejszych struktur czwórnikowych. | ||

| Linia 226: | Linia 226: | ||

</math> | </math> | ||

Macierz łańcuchowa <math>\mathbf{A}\ | Macierz łańcuchowa <math>\mathbf{A}\ </math>, dana jest więc wzorem | ||

: <math> | : <math> | ||

| Linia 271: | Linia 271: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd7.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd7.png|500px]] | ||

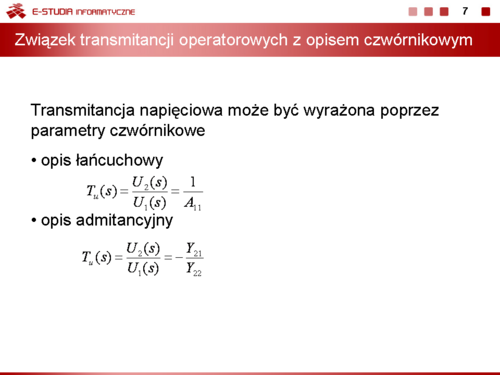

|valign="top"| | |valign="top"|Pokażemy związek opisu transmitancyjnego z parametrami macierzowymi czwórnika. | ||

| Linia 304: | Linia 302: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd8.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd8.png|500px]] | ||

|valign="top"|'''Impedancja wejściowa''' | |valign="top"|'''Impedancja wejściowa''' | ||

| Linia 331: | Linia 329: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd9.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd9.png|500px]] | ||

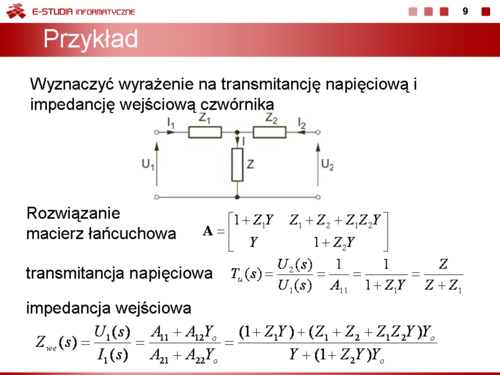

|valign="top"| | |valign="top"|Wyznaczyć wyrażenie na transmitancję napięciową i impedancję wejściową czwórnika z poprzedniego przykładu. | ||

Wyznaczyć wyrażenie na transmitancję napięciową i impedancję wejściową czwórnika z poprzedniego przykładu. | |||

''Rozwiązanie'' | ''Rozwiązanie'' | ||

| Linia 340: | Linia 336: | ||

Macierz łańcuchowa czwórnika ma postać | Macierz łańcuchowa czwórnika ma postać | ||

: <math>A= | : <math>\mathbf{A}= | ||

\begin{bmatrix} | \begin{bmatrix} | ||

1+Z_1Y & Z_1+Z_2+Z_1Z_2Y \\ | 1+Z_1Y & Z_1+Z_2+Z_1Z_2Y \\ | ||

| Linia 351: | Linia 347: | ||

: <math>T_u(s)={U_2(s) \over U_1(s)}={1 \over A_{11}}={1 \over 1+Z_1Y}={Z \over Z+Z_1}</math> | : <math>T_u(s)={U_2(s) \over U_1(s)}={1 \over A_{11}}={1 \over 1+Z_1Y}={Z \over Z+Z_1}</math> | ||

Wobec braku obciążenia czwórnika przez impedancję <math>Z_2</math> nie przepływa prąd, stąd całe napięcie wyjściowe pochodzi z impedancji poprzecznej <math>Z\ | Wobec braku obciążenia czwórnika przez impedancję <math>Z_2</math> nie przepływa prąd, stąd całe napięcie wyjściowe pochodzi z impedancji poprzecznej <math>Z\ </math>, (dzielnik impedancyjny). | ||

Impedancja wejściowa czwórnika przy obciążeniu bramy wyjściowej impedancją <math>Z_0</math> na podstawie | Impedancja wejściowa czwórnika przy obciążeniu bramy wyjściowej impedancją <math>Z_0</math> na podstawie wzoru jest równa | ||

: <math>Z_{we}(s)={U_1(s) \over I_1(s)}={A_{11}+A_{12}Y_0 \over A_{21}+A_{22}Y_0} | : <math>Z_{we}(s)={U_1(s) \over I_1(s)}={A_{11}+A_{12}Y_0 \over A_{21}+A_{22}Y_0}={(1+Z_1Y)+(Z_1+Z_2+Z_1Z_2Y)Y_0 \over Y+(1+Z_2Y)Y_0}</math> | ||

Jest ona funkcją wszystkich parametrów układu oraz impedancji obciążenia. | Jest ona funkcją wszystkich parametrów układu oraz impedancji obciążenia. | ||

|} | |} | ||

| Linia 365: | Linia 359: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10.png|500px]] | ||

|valign="top"| | |valign="top"|'''Połączenie łańcuchowe''', zwane również kaskadowym czwórników to takie połączenie , w którym zaciski wejściowe jednego czwórnika są przyłączone do zacisków wyjściowych poprzedniego. Przykład połączenia łańcuchowego dwu czwórników przedstawiony jest na rysunku obok. | ||

'''Połączenie łańcuchowe''' | |||

Łatwo jest pokazać, że macierz łańcuchowa <math>A\ | Łatwo jest pokazać, że macierz łańcuchowa <math>\mathbf{A}\ </math>, czwórników połączonych kaskadowo jest równa iloczynowi macierzy łańcuchowych poszczególnych czwórników tworzących to połączenie | ||

: <math>A= | : <math>\mathbf{A}=\mathbf{A}_1 \cdot \mathbf{A}_2</math> | ||

Przy większej liczbie czwórników połączonych kaskadowo macierz łańcuchowa wypadkowa jest równa iloczynowi macierzy łańcuchowych wszystkich czwórników branych w kolejności ich występowania w łańcuchu. | Przy większej liczbie czwórników połączonych kaskadowo macierz łańcuchowa wypadkowa jest równa iloczynowi macierzy łańcuchowych wszystkich czwórników branych w kolejności ich występowania w łańcuchu. | ||

: <math>A= | : <math>\mathbf{A}=\mathbf{A}_1 \mathbf{A}_2 \cdots \mathbf{A}_n</math> | ||

Należy zwrócić uwagę, że przy mnożeniu macierzy istotna jest kolejność tych macierzy, gdyż w ogólności <math> | Należy zwrócić uwagę, że przy mnożeniu macierzy istotna jest kolejność tych macierzy, gdyż w ogólności <math>\mathbf{A}_1 \cdot \mathbf{A}_2\neq \mathbf{A}_2 \cdot \mathbf{A}_1</math> | ||

|} | |||

<hr width="100%"> | |||

{| border="0" cellpadding="4" width="100%" | |||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10a.png|500px]] | |||

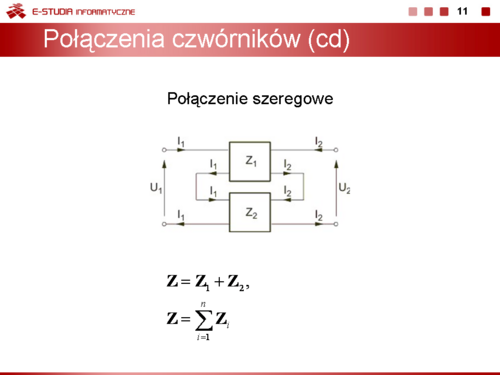

Dwa czwórniki są połączone szeregowo, jeśli spełnione są warunki: | |valign="top"|Dwa czwórniki są '''połączone szeregowo''', jeśli spełnione są warunki: | ||

*prąd wejściowy jednego czwórnika jest równy prądowi wejściowemu drugiego a prąd wyjściowy jednego czwórnika jest równy prądowi wyjściowemu drugiego | *prąd wejściowy jednego czwórnika jest równy prądowi wejściowemu drugiego a prąd wyjściowy jednego czwórnika jest równy prądowi wyjściowemu drugiego | ||

*napięcie wejściowe (wyjściowe) połączenia jest równe sumie napięć wejściowych (wyjściowych) każdego czwórnika. | *napięcie wejściowe (wyjściowe) połączenia jest równe sumie napięć wejściowych (wyjściowych) każdego czwórnika. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych szeregowo, spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu szeregowym czwórników macierz impedancyjna <math>Z\ | Łatwo jest pokazać, że w połączeniu szeregowym czwórników macierz impedancyjna <math>\mathbf{Z}\ </math>, połączenia jest równa sumie macierzy impedancyjnych każdego czwórnika. Oznacza to, że | ||

: <math>Z= | : <math>\mathbf{Z}=\mathbf{Z}_1+\mathbf{Z}_2</math> | ||

Przy większej liczbie czwórników połączonych szeregowo macierz impedancyjna wypadkowa jest równa sumie macierzy impedancyjnych wszystkich czwórników występujących w połączeniu. | Przy większej liczbie czwórników połączonych szeregowo macierz impedancyjna wypadkowa jest równa sumie macierzy impedancyjnych wszystkich czwórników występujących w połączeniu. | ||

: <math>Z=\sum_{i=1}^n | : <math>\mathbf{Z}=\sum_{i=1}^n \mathbf{Z}_i</math> | ||

Kolejność sumowania macierzy impedancyjnych nie odgrywa żadnej roli. | Kolejność sumowania macierzy impedancyjnych nie odgrywa żadnej roli. | ||

|} | |} | ||

| Linia 411: | Linia 398: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd11.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd11.png|500px]] | ||

|valign="top"|''' | |valign="top"|Dwa czwórniki są '''połączone równolegle''', jeśli spełnione są warunki: | ||

*napięcie wejściowe każdego czwórnika jest takie samo, podobnie napięcie wyjściowe | *napięcie wejściowe każdego czwórnika jest takie samo, podobnie napięcie wyjściowe | ||

*prąd wejściowy (wyjściowy) połączenia jest równy sumie prądów wejściowych (wyjściowych) każdego czwórnika. | *prąd wejściowy (wyjściowy) połączenia jest równy sumie prądów wejściowych (wyjściowych) każdego czwórnika. | ||

Ponadto w tym przypadku należy zapewnić spełnienie warunków regularności połączenia zdefiniowanych odpowiednią równością prądów | Ponadto w tym przypadku należy zapewnić spełnienie warunków regularności połączenia zdefiniowanych odpowiednią równością prądów. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych równolegle, spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu równoległym czwórników macierz admitancyjna <math>Y\ | Łatwo jest pokazać, że w połączeniu równoległym czwórników macierz admitancyjna <math>\mathbf{Y}\ </math>, połączenia jest równa sumie macierzy admitancyjnych każdego czwórnika. Oznacza to, że | ||

: <math>Y= | : <math>\mathbf{Y}=\mathbf{Y}_1+\mathbf{Y}_2</math> | ||

Przy większej liczbie czwórników połączonych równolegle macierz admitancyjna wypadkowa jest równa sumie macierzy admitancyjnych wszystkich czwórników występujących w połączeniu. | Przy większej liczbie czwórników połączonych równolegle macierz admitancyjna wypadkowa jest równa sumie macierzy admitancyjnych wszystkich czwórników występujących w połączeniu. | ||

: <math>Y=\sum_{i=1}^n | : <math>\mathbf{Y}=\sum_{i=1}^n \mathbf{Y}_i</math> | ||

Kolejność sumowania macierzy admitancyjnych nie odgrywa żadnej roli. | Kolejność sumowania macierzy admitancyjnych nie odgrywa żadnej roli. | ||

|} | |||

<hr width="100%"> | |||

{| border="0" cellpadding="4" width="100%" | |||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd10b.png|500px]] | |||

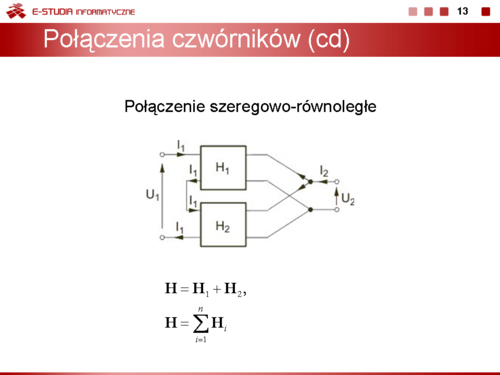

Dwa czwórniki są połączone szeregowo-równolegle, jeśli spełnione są warunki: | |valign="top"|Dwa czwórniki są '''połączone szeregowo-równolegle''', jeśli spełnione są warunki: | ||

*prąd wejściowy każdego czwórnika jest taki sam a napięcie wejściowe połączenia jest równe sumie napięć wejściowych każdego czwórnika | *prąd wejściowy każdego czwórnika jest taki sam a napięcie wejściowe połączenia jest równe sumie napięć wejściowych każdego czwórnika | ||

*prąd wyjściowy połączenia jest równy sumie prądów wyjściowych każdego czwórnika a napięcie wyjściowe obu czwórników jest takie samo. | *prąd wyjściowy połączenia jest równy sumie prądów wyjściowych każdego czwórnika a napięcie wyjściowe obu czwórników jest takie samo. | ||

Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów | Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych szeregowo-równolegle (szeregowo po stronie zacisków wejściowych i równolegle po stronie zacisków wyjściowych), spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu szeregowo-równoległym czwórników macierz hybrydowa <math>H\ | Łatwo jest pokazać, że w połączeniu szeregowo-równoległym czwórników macierz hybrydowa <math>H\ </math>, połączenia jest równa sumie macierzy hybrydowych <math>\mathbf{H}\ </math>, każdego czwórnika. Oznacza to, że | ||

: <math>H= | : <math>\mathbf{H}=\mathbf{H}_1+\mathbf{H}_2</math> | ||

Przy większej liczbie czwórników połączonych szeregowo-równolegle macierz hybrydowa <math>H\ | Przy większej liczbie czwórników połączonych szeregowo-równolegle macierz hybrydowa <math>\mathbf{H}\ </math>,, wypadkowa dla całego połączenia jest równa sumie macierzy hybrydowych <math>\mathbf{H}\ </math>, wszystkich czwórników występujących w połączeniu. | ||

: <math>H=\sum_{i=1}^n | : <math>\mathbf{H}=\sum_{i=1}^n \mathbf{H}_i</math> | ||

Kolejność sumowania macierzy hybrydowych nie odgrywa żadnej roli. | Kolejność sumowania macierzy hybrydowych nie odgrywa żadnej roli. | ||

|} | |} | ||

| Linia 460: | Linia 446: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd12.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd12.png|500px]] | ||

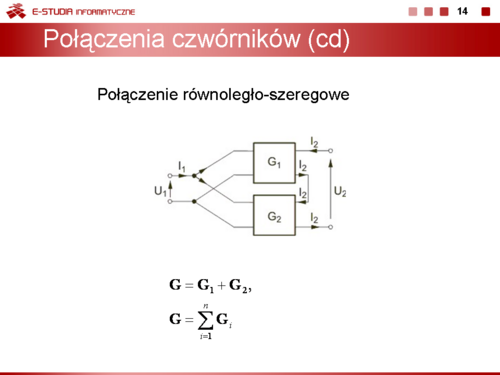

|valign="top"|''' | |valign="top"|Dwa czwórniki są '''połączone równolegle-szeregowo''', jeśli spełnione są warunki: | ||

*napięcie wejściowe każdego czwórnika jest takie samo a prąd wejściowy połączenia jest równy sumie prądów wejściowych każdego czwórnika | *napięcie wejściowe każdego czwórnika jest takie samo a prąd wejściowy połączenia jest równy sumie prądów wejściowych każdego czwórnika | ||

*prąd wyjściowy każdego czwórnika jest taki sam a napięcie wyjściowe połączenia jest równe sumie napięć wyjściowych każdego z nich. | *prąd wyjściowy każdego czwórnika jest taki sam a napięcie wyjściowe połączenia jest równe sumie napięć wyjściowych każdego z nich. | ||

Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów | Ponadto w tym przypadku należy zapewnić spełnienie warunku regularności połączenia zdefiniowanego odpowiednią równością prądów. | ||

Na rysunku obok | Na rysunku obok przedstawiono układ dwu czwórników połączonych równolegle-szeregowo (równolegle po stronie zacisków wejściowych i szeregowo po stronie zacisków wyjściowych), spełniający powyższe warunki. | ||

Łatwo jest pokazać, że w połączeniu równolegle-szeregowym czwórników macierz hybrydowa odwrotna <math>G\ | Łatwo jest pokazać, że w połączeniu równolegle-szeregowym czwórników macierz hybrydowa odwrotna <math>\mathbf{G}\ </math>, połączenia jest równa sumie macierzy hybrydowych <math>G\ </math>, każdego czwórnika. Oznacza to, że | ||

: <math>G= | : <math>\mathbf{G}=\mathbf{G}_1+\mathbf{G}_2</math> | ||

Przy większej liczbie czwórników połączonych równolegle-szeregowo macierz hybrydowa odwrotna <math>G\ | Przy większej liczbie czwórników połączonych równolegle-szeregowo macierz hybrydowa odwrotna <math>\mathbf{G}\ </math>,, wypadkowa dla całego połączenia jest równa sumie macierzy hybrydowych <math>\mathbf{G}\ </math>, wszystkich czwórników występujących w połączeniu. | ||

: <math>G=\sum_{i=1}^n | : <math>\mathbf{G}=\sum_{i=1}^n \mathbf{G}_i</math> | ||

Kolejność sumowania macierzy nie odgrywa żadnej roli. | Kolejność sumowania macierzy nie odgrywa żadnej roli. | ||

|} | |} | ||

| Linia 487: | Linia 470: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd13.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd13.png|500px]] | ||

|valign="top"| | |valign="top"|'''Żyrator''' | ||

'''Żyrator''' | |||

Żyrator jest czwórnikiem opisanym następującą macierzą łańcuchową | Żyrator jest czwórnikiem opisanym następującą macierzą łańcuchową | ||

| Linia 511: | Linia 491: | ||

</math> | </math> | ||

Parametr <math>G_z</math> jest nazywany konduktancją żyracji a <math>R_z=1/G_z</math> rezystancją. Oznaczenia graficzne żyratora przedstawione są na rysunku obok | Parametr <math>G_z</math> jest nazywany konduktancją żyracji a <math>R_z=1/G_z</math> rezystancją. Oznaczenia graficzne żyratora przedstawione są na rysunku obok. | ||

Znak minus występujący przy prądzie wyjściowym wynika z przyjętego zwrotu prądu wyjściowego (do pudełka). Równaniu łańcuchowemu żyratora odpowiada opis admitancyjny o postaci | Znak minus występujący przy prądzie wyjściowym wynika z przyjętego zwrotu prądu wyjściowego (do pudełka). Równaniu łańcuchowemu żyratora odpowiada opis admitancyjny o postaci | ||

| Linia 531: | Linia 511: | ||

</math> | </math> | ||

Najważniejszą własnością żyratora jest przetwarzanie impedancji obciążenia w impedancję odwrotnie proporcjonalną do niej. Rozważmy układ żyratora obciążonego impedancją <math> | Najważniejszą własnością żyratora jest przetwarzanie impedancji obciążenia w impedancję odwrotnie proporcjonalną do niej. Rozważmy układ żyratora obciążonego impedancją <math>Z_o</math>. | ||

Impedancja wejściowa takiego układu zdefiniowana w postaci | Impedancja wejściowa takiego układu zdefiniowana w postaci | ||

| Linia 539: | Linia 519: | ||

<math>A_{11}=0</math>, <math>A_{12}=R_z</math>, <math>A_{21}=G_z</math>, <math>A_{22}=0</math>, więc | <math>A_{11}=0</math>, <math>A_{12}=R_z</math>, <math>A_{21}=G_z</math>, <math>A_{22}=0</math>, więc | ||

: <math>Z_{we}={A_{11}+A_{12} | : <math>Z_{we}={A_{11}+A_{12}Y_o \over A_{21}+A_{22}Y_o}={R_z^2 \over Z_o}</math> | ||

|} | |} | ||

| Linia 545: | Linia 525: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd14.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd14.png|500px]] | ||

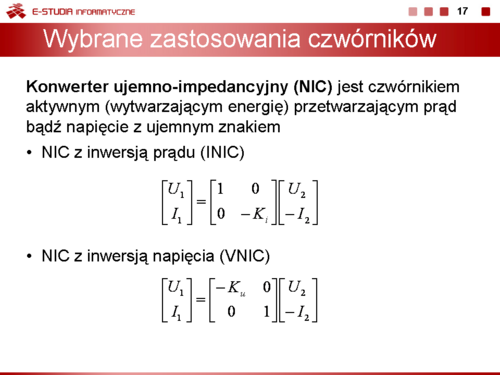

|valign="top"|Impedancja układu żyratora obciążonego impedancją <math> | |valign="top"|Impedancja układu żyratora obciążonego impedancją <math>Z_o</math> jest odwrotnie proporcjonalna do impedancji obciążenia ze współczynnikiem proporcjonalności równym <math>R_z^2</math>. Jeśli żyrator zostanie obciążony kondensatorem o impedancji operatorowej równej <math>Z_o = 1/sC</math> to impedancja wejściowa układu jest równa | ||

: <math>Z_{we}=sR_z^2C</math> | : <math>Z_{we}=sR_z^2C</math> | ||

Jest to postać odpowiadająca ogólnemu opisowi impedancji operatorowej cewki <math>Z_L=sL</math>. Zatem układ żyratora obciążonego pojemnością <math>C\ | Jest to postać odpowiadająca ogólnemu opisowi impedancji operatorowej cewki <math>Z_L=sL</math>. Zatem układ żyratora obciążonego pojemnością <math>C\ </math>, przedstawia sobą cewkę o indukcyjności <math>L\ </math>, | ||

: <math>L=R_z^2C</math> | : <math>L=R_z^2C</math> | ||

Powyższej zależności matematycznej można przyporządkować transformację układową zilustrowaną na rysunku obok | Powyższej zależności matematycznej można przyporządkować transformację układową zilustrowaną na rysunku obok. | ||

Żyrator jako czwórnik jest bardzo łatwo realizowalny w praktyce przy wykorzystaniu układów tranzystorowych lub wzmacniaczy operacyjnych. Z tego względu układy wykorzystujące żyratory są powszechnie stosowane w układach elektronicznych (np. filtrach) eliminując z nich cewki, trudno realizowalne w technologii scalonej. | Żyrator jako czwórnik jest bardzo łatwo realizowalny w praktyce przy wykorzystaniu układów tranzystorowych lub wzmacniaczy operacyjnych. Z tego względu układy wykorzystujące żyratory są powszechnie stosowane w układach elektronicznych (np. filtrach) eliminując z nich cewki, trudno realizowalne w technologii scalonej. | ||

| Linia 562: | Linia 542: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd15.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd15.png|500px]] | ||

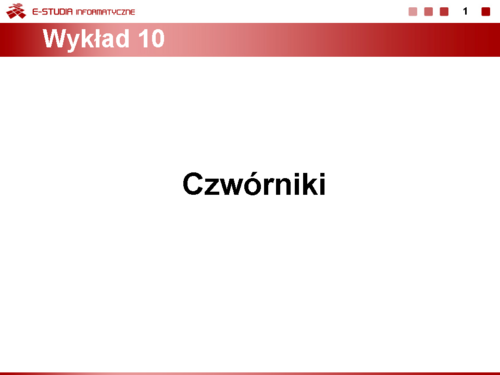

|valign="top"|'''Konwerter ujemno-impedancyjny (NIC)''' | |valign="top"|'''Konwerter ujemno-impedancyjny (NIC)''' | ||

| Linia 603: | Linia 583: | ||

Parametr <math>K\ | Parametr <math>K\ </math>, (<math>K_i</math> dla konwertera ujemno-impedancyjnego prądu oraz <math>K_u</math> dla konwertera ujemno-impedancyjnego napięcia) jest współczynnikiem przetwarzania bądź prądu bądź napięcia. W konwerterze INIC prąd wejściowy jest proporcjonalny do prądu wyjściowego z ujemnym współczynnikiem proporcjonalności <math>–K_i</math> przy niezmienionej wartości napięcia wejściowego. W konwerterze VNIC napięcie wejściowe jest proporcjonalne do napięcia wyjściowego z ujemnym współczynnikiem proporcjonalności <math>–K_u</math> przy niezmienionym prądzie wejściowym. | ||

|} | |} | ||

| Linia 609: | Linia 589: | ||

{| border="0" cellpadding="4" width="100%" | {| border="0" cellpadding="4" width="100%" | ||

|valign="top" width="500px"|[[Grafika:PEE_M10_Slajd16.png]] | |valign="top" width="500px"|[[Grafika:PEE_M10_Slajd16.png|500px]] | ||

|valign="top"|Konwerter impedancyjny przetwarza impedancję obciążenia w impedancję wejściową z ujemnym znakiem. Rozważmy układ konwertera INIC obciążonego impedancją <math> | |valign="top"|Konwerter impedancyjny przetwarza impedancję obciążenia w impedancję wejściową z ujemnym znakiem. Rozważmy układ konwertera INIC obciążonego impedancją <math>Z_o</math>, przedstawiony na rysunku obok. | ||

Wykorzystując równania konwertera i uwzględniając równanie opisujące obciążenie <math>U_o=Z_o(-I_2)=U_2</math> impedancja wejściowa układu dana jest zależnością | |||

: <math>Z_{we}={U_1 \over I_1}={U_2 \over -K_i(-I_2)}=-{Z_o \over K_i}</math> | |||

Jak z powyższego równania wynika konwerter ujemno-impedancyjny obciążony impedancją <math>Z_o</math> reprezentuje sobą (z punktu widzenia wejścia) impedancję ujemną <math>-{Z_o \over K_i}</math>. Podobną własność ma konwerter ujemno-impedancyjny napięcia (VNIC). | |||

Cecha ta może być wykorzystana do realizacji rezystancji ujemnej. Mianowicie przyjmując obciążenie konwertera rezystancją <math>Z_o=R_o</math> otrzymuje się impedancję wejściową równą <math>Z_{we}=-R_o/K_i</math>. Należy pamiętać, że ujemna rezystancja zastosowana samodzielnie prowadzi do niestabilności układu (wobec ujemnych wartości rezystancji bieguny układu znajdą się w prawej półpłaszczyźnie). Z tego względu stosuje się ją zwykle w specjalnych połączeniach z innymi elementami obwodowymi zapewniającymi stabilne działanie układu. | |||

|} | |} | ||

<hr width="100%"> | <hr width="100%"> | ||

'''Zadania sprawdzjące''' | |||

| Linia 649: | Linia 628: | ||

Macierz admitancyjna | Macierz admitancyjna | ||

: <math>Y= | : <math>\mathbf{Y}= | ||

\begin{bmatrix} | \begin{bmatrix} | ||

Y_1+Y_3 & -Y_3 \\ | Y_1+Y_3 & -Y_3 \\ | ||

| Linia 656: | Linia 635: | ||

</math> | </math> | ||

---- | |||

''Zadanie 10.2'' | ''Zadanie 10.2'' | ||

Aktualna wersja na dzień 12:01, 5 wrz 2023

|

Zadania sprawdzjące

Zadanie 10.1

Wyznaczyć macierzowy opis czwórnikowy czwórnika typu o strukturze podanej na rysunku poniżej.

Rozwiązanie

Układ równań Kirchhoffa opisujących obwód

Równania czwórnikowe

Macierz admitancyjna

Zadanie 10.2

Wyznaczyć macierz łańcuchową czwórnika odpowiadającego obwodowi z rysunku poniżej. Określić na tej podstawie transmitancję napięciową układu.

Rozwiązanie

Z równań Kirchhoffa dla obwodu otrzymuje się

Opis łańcuchowy czwórnika

Transmitancja napięciowa określana przy założeniu jest równa